# AltaCore-ARINC™ ARINC (RX & TX) Protocol Engine Specifications-Users Manual

Part Number: 14102-00000-E7 Cage Code: 4RK27 • NAICS: 334118

Alta Data Technologies LLC 4901 Rockaway Blvd., Building A Rio Rancho, NM 87124 USA (tel) 505-994-3111 • www.altadt.com

| CUSTOMER NOTES: |  |  |

|-----------------|--|--|

|                 |  |  |

|                 |  |  |

|                 |  |  |

|                 |  |  |

|                 |  |  |

|                 |  |  |

|                 |  |  |

|                 |  |  |

|                 |  |  |

|                 |  |  |

|                 |  |  |

|                 |  |  |

|                 |  |  |

|                 |  |  |

|                 |  |  |

|                 |  |  |

OLIOTOMED MOTEO

# **Revision Control History**

Rev E7 Release Date: 11 March 2015

#### Note to the Reader and End-User:

This document is provided for information only and is © Alta Data Technologies LLC 2011-14. While Alta strives to provide the most accurate information, there may be errors and omissions in this document. Alta disclaims all liability in document errors and any product usage. By using an Alta product, the customer or end user agrees (1) to accept Alta's Standard Terms and Conditions of Sale, Standard Warranty and Software License and (2) to not hold Alta Members, Employees, Contractors or Sales & Support Representatives responsible for any loss or legal liability, tangible or intangible, from any document errors or any product usage.

The product described in this document is not US ITAR controlled. Use of Alta products or documentation in violation of local usage, waste discard and export control rules, or in violation of US ITAR regulations, voids product warranty and shall not be supported. This document may be distributed to support government programs and projects. Third party person, company or consultant distribution is not allowed without Alta's written permission.

AltaCore-ARINC, AltaCore-ARINC-1553, AltaCore-ARINC, AltaAPI, AltaView and AltaRTVal are Trademarks of Alta Data Technologies LLC, Rio Rancho, New Mexico USA

#### Contact:

We welcome comments and suggestions. Please contact us at 888-429-1553 (toll free in US) or 505-994-3111 or visit our web site for support submit forms at www.altadt.com or email us at alta.info@altadt.com or alta.support@altadt.com.

# AltaCore-ARINC™

# **Table of Contents**

| AltaCore-ARINC™                                                               | iii |

|-------------------------------------------------------------------------------|-----|

| Table of Contents                                                             | iii |

| AltaCore-ARINC™                                                               | 1   |

| Introduction                                                                  | 1   |

| Terminology                                                                   | 1   |

| AltaCore-ARINC Architecture and Document Basics                               | 2   |

| Memory Mapped Architecture                                                    | 2   |

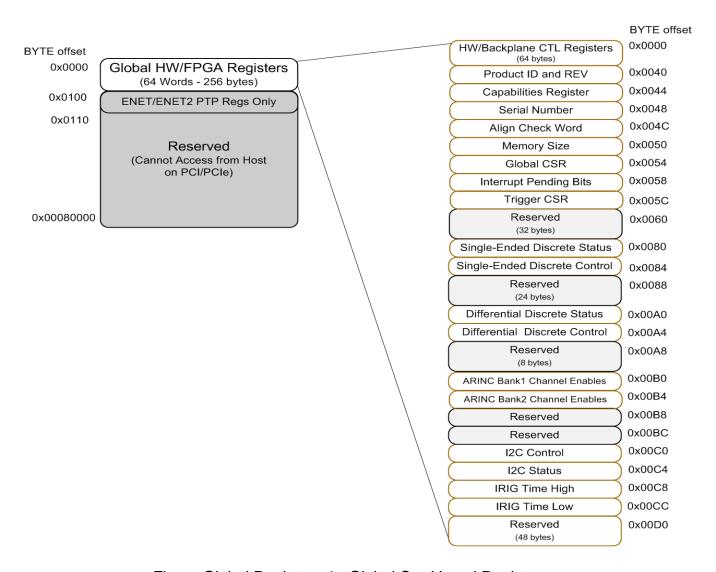

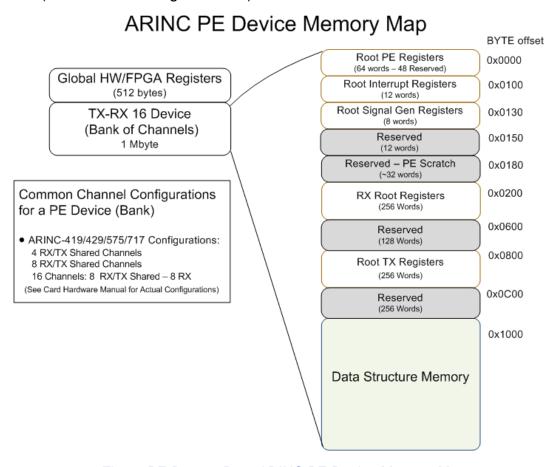

| Figure Intro-1: Basic <i>AltaCore-ARINC</i> Memory Map                        | 3   |

| Global Registers                                                              | 3   |

| RX and TX Buffer and Interrupt Data Structures: Root verses Extended Memory . | 3   |

| Memory Offset References                                                      | 4   |

| Packed Word and Bit Data Structures                                           | 4   |

| Execution Times, Channel Timing, Time Tags                                    | 4   |

| Reserve Bits and Words                                                        | 4   |

| Figure Color Codes                                                            | 5   |

| AltaCore-ARINC Global Registers (Card Level)                                  | 6   |

| Global Card Level Registers                                                   | 6   |

| HW/Backplane CTL Registers (16 words - 0x00000000-0000000F)                   | 6   |

| Figure Global Registers-2: Device Global Registers                            | 8   |

| Figure Global Registers-2A: Device Global Registers                           | 8   |

| Product ID and Rev: 0x00000040                                                | 9   |

| Capabilities Register: 0x00000044                                             | 9   |

| Bits 0-5: 1553 Channel Enables*                                               | 9   |

| Bit 8: Flash Read Capable                                                     | 9   |

| Bit 9: Variable Voltage Capable*                                              | 9   |

| Bit 10: Multi-Function Capable*                                               | 9   |

| Bit 11: IRIG Capable                                                          | 9   |

| Bit 14: <i>AltaRTVal</i> Capable*                                             | 9   |

|   | Bit 15: <i>AltaView</i> Capable                                               | 9    |

|---|-------------------------------------------------------------------------------|------|

|   | Bit 24: ARINC Bank1 Capable                                                   | 10   |

|   | Bit 25: ARINC Bank2 Capable                                                   | 10   |

| S | erial Number: 0x00000048                                                      | 10   |

| A | lignment Test Register: 0x0000004C                                            | 10   |

| V | lemory Size: 0x00000050                                                       | 10   |

| G | Global CSR: W: 0x00000054                                                     | . 10 |

|   | Bit 0: Clear All Time Tags: W                                                 | 10   |

|   | Bit 1: Set all Time Tags: W                                                   | 11   |

|   | Bit 2: Latch Global IRIG Time: W                                              | 11   |

|   | Bit 3: IRIG Detected: R                                                       | 11   |

|   | Bit 4: IRIG Lock: R                                                           | 11   |

|   | Bit 5: Force Ext Trigger In: W                                                | 11   |

|   | Bit 12: Ext Clk In Src=RS-485: W                                              | 12   |

|   | Bit 13: Ext Clk In Src=TTL: W                                                 | 12   |

|   | Bit 16: Ext Clk Out Src=RS-485: W                                             | 12   |

|   | Bit 17: Ext Clk Out Src=TTL: W                                                | 12   |

|   | Bit 18: Ext Clk Out=1 MHz: W                                                  | 13   |

|   | Bit 19: Ext Clk Out=5 MHz: W                                                  | 13   |

|   | Bit 20: Ext Clk Out=10 MHz: W                                                 | 13   |

|   | Bit 26: Flash Write Protect: R                                                | 13   |

|   | Bit 30: user/API LED1: W                                                      | 13   |

|   | Bit 31: user/API LED2: W                                                      | 13   |

|   | tummary of Multi Application verses Single Application Interrupt Options with | 13   |

|   | Multi Applications Scenarios:                                                 | 13   |

|   | Single Application Scenarios:                                                 |      |

| G | Global Interrupt Register: W: 0x00000058                                      | 13   |

|   | Bits 0-3: Interrupt Pending                                                   |      |

|   | Bits 16-19: Interrupt Latched: W                                              |      |

|   | Rit 31: Latch Hardware Int: W                                                 | 15   |

|    | Trigger CSR: W: 0x0000005C                            | . 15 |

|----|-------------------------------------------------------|------|

|    | Bit 15-0: Trigger Output Control: W                   | . 15 |

|    | Bit 31-16: Trigger Input Status:                      | . 15 |

|    | Discrete Configurations – See Product Hardware Manual | . 15 |

|    | Single-Ended Discrete Status Register: 0x00000080     | . 15 |

|    | Single-Ended Discrete Output Register: W: 0x00000084  | . 16 |

|    | Differential Discrete Status Register: 0x000000A0     | . 16 |

|    | Differential Discrete Output Register: W: 0x000000A4  | . 16 |

|    | Bit 15-0: Output Control: W                           | . 16 |

|    | Bit 31-16: Output Enable: W                           | . 16 |

|    | I2C Control Register: W: 0x00000C0                    | . 16 |

|    | I2C Status Register: 0x000000C4                       | . 16 |

|    | IRIG Time High: 0x000000C8                            | . 16 |

|    | IRIG Time Low: 0x000000CC                             | . 17 |

|    | IRIG Code Formats                                     | . 17 |

|    | PTP IEEE-1588 Registers: 0x0100-0x010C                | . 17 |

| 4/ | taCore-ARINC: Root PE Device/Bank Registers           | . 18 |

|    | Introduction                                          | . 18 |

|    | Figure PE Root-1: Root ARINC PE Device Memory Map     | . 18 |

|    | Figure PE Root-2: Root PE Registers                   | . 19 |

|    | Root PE Control Word: W: 0x0000                       | . 19 |

|    | Bit 0: HW Interrupt On: W                             | . 19 |

|    | Bit 4: Signal Generator Mode On: W                    | . 20 |

|    | Bit 5: Clock (CLK) Trigger Enable: W                  | . 20 |

|    | Bit 6: Force External Trigger In: W                   | . 20 |

|    | Bit 7: Force External Trigger Out: W                  | . 20 |

|    | Bit 8: Read IRIG Time                                 | . 20 |

|    | Bit 9: Zero Time-Tag: W                               | . 21 |

|    | Bit 10: Set Time-Tag: W                               | . 21 |

|    | Bit 11: Read Time-Tag: W                              | . 21 |

|    | Bit 12: Use External Signal:W                         | . 21 |

| Bit 13: Ext Input Clk = 1 Mhz                 | 21 |

|-----------------------------------------------|----|

| Bit 14: Ext Input Clk = 5 Mhz                 | 21 |

| Bit 15: Ext Input Clk = 10 Mhz                | 22 |

| Bit 20: PB Time Set: W                        | 22 |

| Bit 21: PB Time Read: W                       | 22 |

| Bit 22: Trigger In Low to High: W             | 22 |

| Bit 23: PB On: W                              | 22 |

| Bit 24: Do Not Reset PB Clock at Start: W     | 22 |

| Bit 25: Skip PXPs with Time Back-up: W        | 22 |

| Bit 26: ENET APMP On – ENET-A429 ONLY         | 22 |

| Bit 27: APMP IRIG On – ENET-A429 Only         | 23 |

| Bit 28: APMP INTVL On – ENET-A429 Only        | 23 |

| Bit 29: INT on BIT Fail                       | 23 |

| Bit 30: Run Initiated BIT                     | 23 |

| Bit 31: Reset Channel                         | 23 |

| Root PE Status Word: 0x0004                   | 23 |

| Bit 0: Interrupt Pending: W                   | 23 |

| Bit 10: IRIG Detected                         | 24 |

| Bit 11: IRIG Lock                             | 24 |

| Bits 16-20: Bit Time Tag                      | 24 |

| Bit 26: Flash Read Enable                     | 24 |

| Bit 27: Signal Capture Enabled                | 24 |

| Root PE Product ID & Version: 0x0008          | 25 |

| Root PE RX/TX Enables: W: 0x000C              | 25 |

| Root Total RxPs Received: W: 0x0014           | 25 |

| Root Total TxPs Transmitted: W: 0x0014        | 25 |

| Root Time High & Time Low: W: 0x001C/20       | 25 |

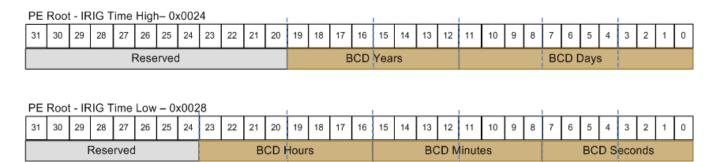

| Root IRIG Time High & Low: 0x0024/28          | 25 |

| Figure Root PE-3: IRIG Time High & Low Format | 26 |

| Root BIT Status: 0x002C                       | 26 |

| Bit 0: Encoder/Decoder Test Failure           | 26 |

| Bit 1: Memory Test Failure                    | 26 |

|-----------------------------------------------|----|

| Bit 2: Processor Test Failure                 | 27 |

| Bit 3: Time-Tag Test Failure                  | 27 |

| Bit 24: POST BIT Failure                      | 27 |

| Bit 25: Periodic BIT Failure                  | 27 |

| Bit 26: Initiated BIT Failure                 | 27 |

| Bit 28: POST BIT In-Progress                  | 27 |

| Bit 29: Periodic BIT In-Progress              | 27 |

| Bit 30: Initiated BIT In-Progress             | 27 |

| Root Signal Capture CSR Channel A: 0x0034     | 27 |

| Signal Capture Discussion                     | 27 |

| Bit 0: Trigger on Any Activity: W             | 28 |

| Bit 1: Trigger on Label/SDI – Not Implemented | 28 |

| Bits 6-15: Label/SDI Value                    | 28 |

| Bit 30: FIFO Not Empty                        | 28 |

| Bit 31: Data Ready: W                         | 28 |

| Root Signal Data A: 0x0038                    | 29 |

| Bits 0-7: Data 0                              | 29 |

| Bits 8-15: Data 1                             | 29 |

| Bits 16-23: Data 2                            | 29 |

| Bits 24-31: Data 3                            | 29 |

| Root Signal Capture CSR RX Channel 0: 0x003C  | 29 |

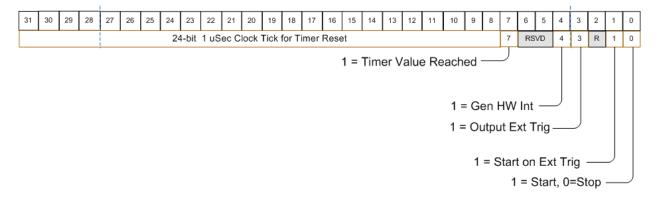

| Root Interval Timer: 0x004C                   | 29 |

| Figure Root PE-4: Interval Timer Register     | 29 |

| Bit 0: Timer Start/Stop: W                    | 29 |

| Bit 1: Start on Ext Trig: W                   | 30 |

| Bit 3: Output Ext Trig: W                     | 30 |

| Bit 4: Gen HW Int: W                          | 30 |

| Bits 7: Time Value Reached: W                 | 30 |

| Bits 8-31: Time Interval Reset Value: W       | 30 |

| PTP IEEE-1588 Registers: 0x00C0-0x00F8        | 30 |

| 4 | ItaCore-ARINC: Transmit (TX)                                                 | 31 |

|---|------------------------------------------------------------------------------|----|

|   | TX Data Structures                                                           | 31 |

|   | TX Basics                                                                    | 31 |

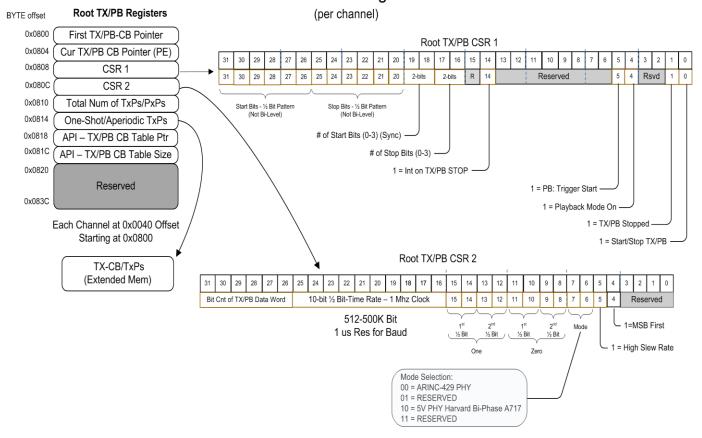

|   | Figure TX-1: Root TX Registers and Root TX CSR                               | 32 |

|   | Root First TX-CB Address: W: 0x0800                                          | 32 |

|   | Root Current TX-CB Pointer: W: 0x0804                                        | 32 |

|   | Root TX CSR1: W: 0x0808                                                      | 32 |

|   | Bit 0: Start/Stop TX: W                                                      | 33 |

|   | Bit 1: TX Stopped                                                            | 33 |

|   | Bit 4: TX Playback On: W – See Playback Section for Details                  | 33 |

|   | Bit 5: Do Not Reset PB Clock at Start: W - See Playback Section for Details  | 33 |

|   | Bit 6: PB: Skip PxPs With Time Back-Up: W - See Playback Section for Details | 33 |

|   | Bit 14: Interrupt of TX Stopped: W                                           | 34 |

|   | Bits 16-17: Number of Stop Bits: W – NI in the version                       | 34 |

|   | Bits 18-19: Number of Start Bits: W – NI in the version                      | 34 |

|   | Bits 20-25: Stop Bits - ½ Bit Pattern: W – NI in the version                 | 34 |

|   | Bits 26-31: Start Bits - ½ Bit Pattern: W – NI in the version.               | 34 |

|   | Root TX CSR2: W: 0x080C                                                      | 34 |

|   | Bit 4: 1=MSB First: W                                                        | 35 |

|   | Bit 5: 1= High Slew Rate: W                                                  | 35 |

|   | Mode Encoding Bits                                                           | 35 |

|   | Bits 6 & 7 = 0x0: Normal ARINC-429 Physical Receiver                         | 35 |

|   | Bits 6 & 7 = 0x2: 5V Harvard Bi-Phase (717) Only – Two TX Channels           | 35 |

|   | Bit Encoding                                                                 | 35 |

|   | Bits 8-11: Logic Zero Encoding: W                                            | 36 |

|   | Bits 8-9: Zero - 2 <sup>nd</sup> ½ Bit: W                                    | 36 |

|   | Bits 10-11: Zero - 1 <sup>st</sup> ½ Bit: W                                  | 36 |

|   | Bits 12-15: Logic One Encoding: W                                            | 36 |

|   | Bits 12-13: One - 2 <sup>nd</sup> ½ Bit: W                                   | 36 |

|   | Bits 14-15: One - 1 <sup>st</sup> ½ Bit: W                                   | 36 |

|   | Programming TX Rit (Raud) Rate                                               | 36 |

| Bits 16-25: ½ Bit-Time Rate: W             | 36 |

|--------------------------------------------|----|

| Programming TX Bits Per Word (word length) | 37 |

| Bits 26-31: Bit Count for TX Data Word: W  | 37 |

| Root One-Shot/Aperiodic TxP: W: 0x0814     | 37 |

| Root API - TX-CB Table Pointer: W: 0x0818  | 37 |

| Root API - TX-CB Table Size: W: 0x081C     | 37 |

| Transmit Control Blocks (TX-CB)            | 38 |

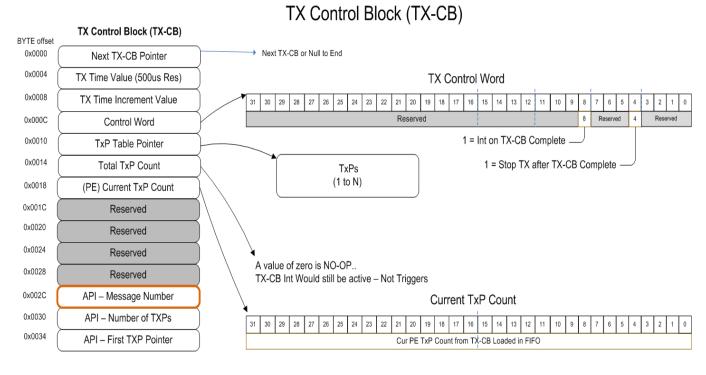

| Figure TX-2: TX Control Block (TX-CB)      | 38 |

| Next TX-CB Pointer: W: 0x0000              | 39 |

| TX Time Value: W: 0x0004                   | 39 |

| TX Time Increment: W: 0x0008               | 39 |

| Control Word: W: 0x000C                    | 39 |

| Bit 4: 1=Stop TX after TxP Complete: W     | 40 |

| Bit 8: 1=Interrupt on TxP Complete: W      | 40 |

| TxP Table Pointer: W: 0x0010               | 40 |

| TxP Count: W: 0x0014                       | 40 |

| (PE) Current TxP Count: 0x0018             | 40 |

| API – TxP Number: 0x002C                   | 41 |

| API – Number of TxPs: 0x0030               | 41 |

| API – First TxP Pointer: 0x0034            | 41 |

| Transmit Data Table                        | 41 |

| TxP: Transmit Packet Data Structure        | 41 |

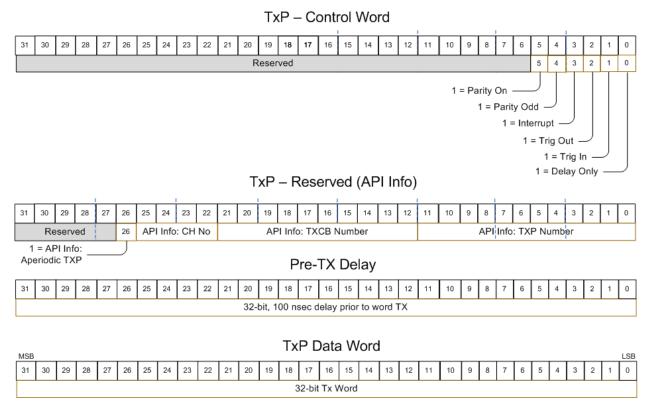

| Figure TX-3: Transmit Packet (TxP)         | 42 |

| TxP Control Word: W: 0x0000                | 42 |

| Bit 0: 1=Delay Only: W                     | 42 |

| Bit 1: 1=Trig In: W                        | 42 |

| Bit 2: 1=Trig Out: W                       | 43 |

| Bit 3: 1=Interrupt: W                      | 43 |

| Bit 4: 1 = Parity On: W                    | 43 |

| Bit 5: 1=Parity Odd: W                     | 43 |

| TxP Word 2 – Reserved (API) Info: 0x0004   | 43 |

|   | TxP Time Gap: W: 0x0008                                                | 43 |

|---|------------------------------------------------------------------------|----|

|   | TxP Data Word: W: 0x000C                                               | 43 |

| 4 | ltaCore-ARINC: Playback (PB)                                           | 45 |

|   | PB Data Structures                                                     | 45 |

|   | PB Basics                                                              | 45 |

|   | Playback Transmission Timing                                           | 45 |

|   | PXP Timing Discussion – Relative Timing                                | 46 |

|   | PXP Timing Discussion – Absolute Timing (AT)                           | 46 |

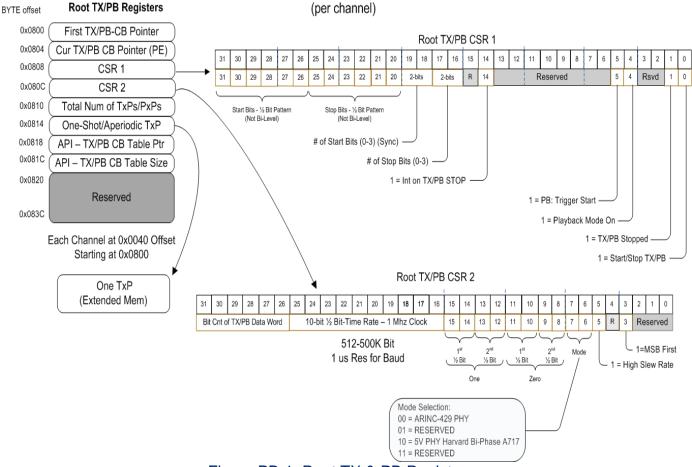

|   | Figure PB-1: Root TX & PB Registers                                    | 47 |

|   | Root First PB-CB Address: W: 0x0800                                    | 47 |

|   | Root Current PB-CB Pointer: W: 0x0804                                  | 47 |

|   | Root TX/PB CSR1: W: 0x0808                                             | 48 |

|   | Bit 0: Start/Stop TX/PB: W                                             | 48 |

|   | Bit 1: TX/PB Stopped                                                   | 49 |

|   | Bit 4: TX Playback On: W                                               | 49 |

|   | Bit 5: PB: Trigger Start: W                                            | 49 |

|   | Bit 14: Interrupt of TX Stopped: W                                     | 49 |

|   | Bits 16-17: Number of Stop Bits: W – NI in the version                 | 49 |

|   | Bits 18-19: Number of Start Bits: W – NI in the version                | 49 |

|   | Bits 20-25: Stop Bits - ½ Bit Pattern: W – NI in the version           | 50 |

|   | Bits 26-31: Start Bits - ½ Bit Pattern: W – NI in the version          | 50 |

|   | Root TX/PB CSR2: W: 0x080C                                             | 50 |

|   | Bit 4: 1=MSB First: W                                                  | 50 |

|   | Bit 5: 1= High Slew Rate: W                                            | 50 |

|   | Mode Encoding Bits                                                     | 50 |

|   | Bits 6 & 7 = 0x0: Normal ARINC-429 Physical Receiver (NA for Playback) | 50 |

|   | Bits 6 & 7 = 0x2: 5V Harvard Bi-Phase (717) Only – Two TX Channels     | 50 |

|   | Bit Encoding                                                           | 51 |

|   | Bits 8-11: Logic Zero Encoding: W                                      | 51 |

|   | Bits 8-9: Zero - 2 <sup>nd</sup> ½ Bit: W                              | 51 |

|   | Rits 10-11: Zero - 1 <sup>st</sup> ½ Rit: W                            | 51 |

|   | Bits 12-15: Logic One Encoding: W                          | . 51 |

|---|------------------------------------------------------------|------|

|   | Bits 12-13: One - 2 <sup>nd</sup> ½ Bit: W                 | . 52 |

|   | Bits 14-15: One - 1 <sup>st</sup> ½ Bit: W                 | . 52 |

|   | Programming TX Bit (Baud) Rate                             | . 52 |

|   | Bits 16-25: ½ Bit-Time Rate: W                             | . 52 |

|   | Programming TX Bits Per Word (word length)                 | . 52 |

|   | Bits 26-31: Bit Count for TX Playback Data Word: W         | . 52 |

|   | Root API - PB-CB Table Pointer: W: 0x0818                  | . 52 |

|   | Root API - PB-CB Table Size: W: 0x081C                     | . 53 |

|   | Playback Control Blocks (PB-CB)                            | . 54 |

|   | Figure PB-2: Playback Control Block (PB-CB) and PXP Format | . 54 |

|   | Next PB-CB Pointer: W: 0x0000                              | . 54 |

|   | Control Word: W: 0x000C                                    | . 55 |

|   | Bit 8: 1=Interrupt on PBCB Complete: W                     | . 55 |

|   | PxP Table Pointer: W: 0x0010                               | . 55 |

|   | PxP Count: W: 0x0014                                       | . 55 |

|   | (PE) Current PxP Count: 0x0018                             | . 55 |

|   | API – PxP Number: 0x002C                                   | . 55 |

|   | API – Number of PxPs: 0x0030                               | . 56 |

|   | API – First PxP Pointer: 0x0034                            | . 56 |

|   | Playback Data Table                                        | . 56 |

|   | Playback Data Packets (PxPs)                               | . 56 |

|   | PxP Control/Status1: W: 0x0000                             | . 56 |

|   | PxP Time Stamp Words (High/Low): 0x0004 & 0x0008           | . 56 |

|   | PxP Data Word                                              | . 56 |

| Α | ItaCore-ARINC: Signal Generator (SG)                       | . 58 |

|   | Signal Generator                                           | . 58 |

|   | Overview of Signal Generation                              | . 58 |

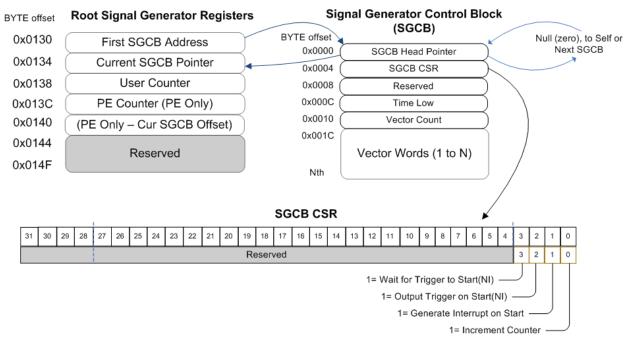

|   | Figure SG-1: Signal Generator Data Structures              | . 58 |

|   | Root PE Signal Generator Control Bits                      | . 59 |

|   | 2-Rit Ri-l evel Vectors                                    | 59   |

|     | Root Signal Generator Registers                                        | 59 |

|-----|------------------------------------------------------------------------|----|

|     | Root First SGCB Address: W: 0x0130                                     | 59 |

|     | Root Current Signal Generator Address: W: 0x0134                       | 59 |

|     | Root Signal Generator Count: W: 0x0138                                 | 60 |

|     | Root PE Count: W: 0x013C                                               | 60 |

|     | Root PE Current Vector Location: 0x0140                                | 60 |

| ,   | Signal Generator Control Blocks (SGCB) – Extended Memory               | 60 |

|     | Next SGCB Pointer: W: 0x0000                                           | 60 |

| ,   | SGCB Control and Status Register: W: 0x0004                            | 60 |

|     | Bit 0: Increment Counter: W                                            | 60 |

|     | Bit 1: Generate Interrupt on Start: W                                  | 61 |

|     | Bit 2: Output Trigger: W – Not Implemented                             | 61 |

|     | Bit 3: Input Trigger Start: W – Not Implemented                        | 61 |

|     | Bits 16-20: Channel Selection Bits: W                                  | 61 |

| (   | Gap Time: W: 0x000C                                                    | 61 |

| ,   | Vector Count: W: 0x0010                                                | 61 |

| ,   | SGCB Vector Bit Words: W: 0x0014-Variable                              | 62 |

| Αli | taCore-ARINC: Receive (RX)                                             | 63 |

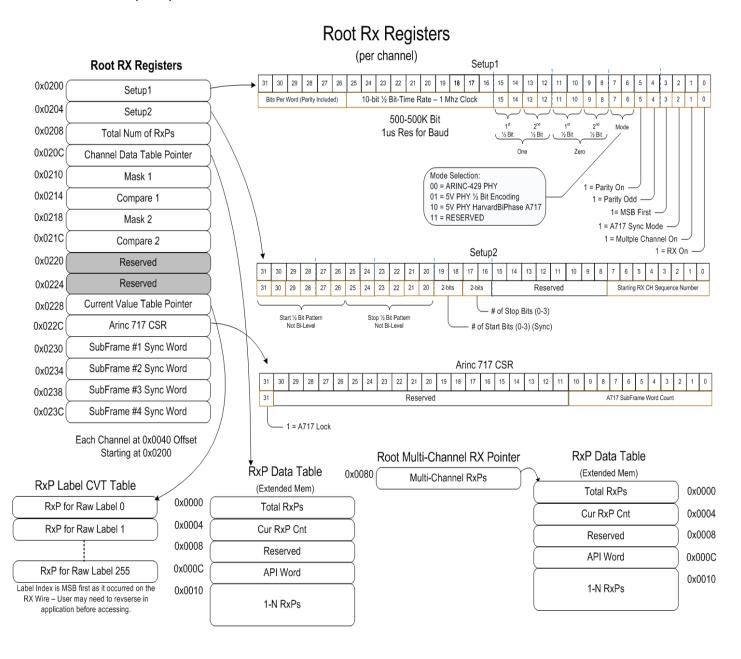

|     | Figure RX-1: Root RX Setup and Pointer Registers                       | 63 |

|     | Root RX Setup Registers: W: 0x0200-0x05FC                              | 64 |

|     | Root Setup1: W: 0x0200 (each channel is 0x0040 Offset to 0x0200)       | 64 |

|     | Bit 0: RX On: W                                                        | 64 |

|     | Bit 1: MC On (Multi-Channel RX): W                                     | 65 |

|     | Bit 2: A717 Mode On: W                                                 | 65 |

|     | Bit 3: 1=MSB First: W                                                  | 65 |

|     | Bit 4: 1 = Parity On: W                                                | 65 |

|     | Bit 5: 1=Parity Odd: W                                                 | 65 |

|     | Mode Decoding Selection                                                | 65 |

|     | Bits 6 & 7 = 0x0: Normal ARINC-429 Physical Receiver                   | 65 |

|     | Bits 6 & 7 = 0x1: 5V Comparator Receiver                               | 65 |

|     | Bits 6 & 7 = 0x2: 5V Comparator Receiver – Harvard Bi-Phase (717) Only | 66 |

| Bit Encoding                                                  |    |

|---------------------------------------------------------------|----|

| Bits 8-11: Logic Zero Encoding: W                             | 66 |

| Bits 8-9: Zero - 2 <sup>nd</sup> ½ Bit: W                     | 67 |

| Bits 10-11: Zero - 1 <sup>st</sup> ½ Bit: W                   | 67 |

| Bits 12-15: Logic One Encoding: W                             | 67 |

| Bits 12-13: One - 2 <sup>nd</sup> ½ Bit: W                    | 67 |

| Bits 14-15: One - 1 <sup>st</sup> ½ Bit: W                    | 67 |

| RX Bit (Baud) Rate                                            | 67 |

| Bits 16-25: Bit Rate (1/2 bit time): W                        | 67 |

| Bits 26-31: Bits Per Word (Including Parity): W               | 67 |

| Root Setup2: W: 0x0004                                        | 68 |

| Bits 0-7: Starting Sequence Number: W                         | 68 |

| Bits 16-17: Number of Stop Bits: W – NI in the version        | 68 |

| Bits 18-19: Number of Start Bits: W – NI in the version       | 68 |

| Bits 20-25: Stop Bits - ½ Bit Pattern: W – NI in the version  | 68 |

| Bits 26-31: Start Bits - ½ Bit Pattern: W – NI in the version | 69 |

| Root Total Num of RxPs: W: 0x0008                             | 69 |

| Root Channel Data Table Pointer: W: 0x000C                    | 69 |

| Root Channel Mask1: W: 0x00010                                | 69 |

| Root Channel Compare1: W: 0x0014                              | 69 |

| Root Channel Mask2: W: 0x0018                                 | 69 |

| Root Channel Compare2: W: 0x001C                              | 69 |

| RESERVED - 0x0020-0024                                        | 70 |

| Root Current Value Table (CVT) Pointer: W: 0x0028             | 70 |

| Root A717 CSR: W: 0x002C                                      | 70 |

| Bits 0-10: SubFrame Word Count: W                             | 70 |

| Bit 31: A717 Lock                                             | 70 |

| ARINC-717 SubFrame Sync Words                                 | 70 |

| Root SubFrame Sync Word1: W: 0x0030                           | 70 |

| Root SubFrame Sync Word2: W: 0x0034                           | 70 |

| Root SubFrame Svnc Word3: W: 0x0038                           | 71 |

| Root SubFrame Sync Word4: W: 0x003C                           | 71 |

|---------------------------------------------------------------|----|

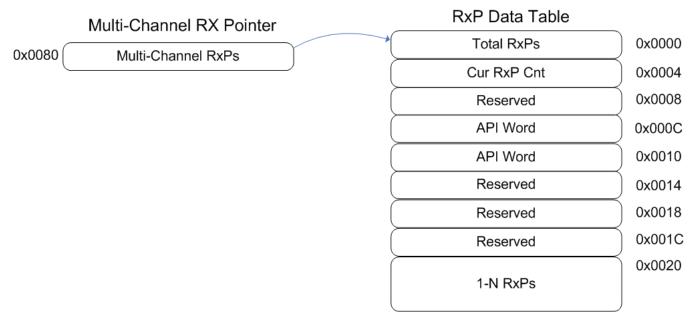

| Root Multi-Channel RX Pointer: W: 0x0080                      | 71 |

| Figure RX-2: Root Multi Channel RX Pointer – RxP Data Table   | 71 |

| RxP Data Tables: W                                            | 71 |

| Total RxP Count: W: 0x0000                                    | 72 |

| Current RxP Count: 0x0004                                     | 72 |

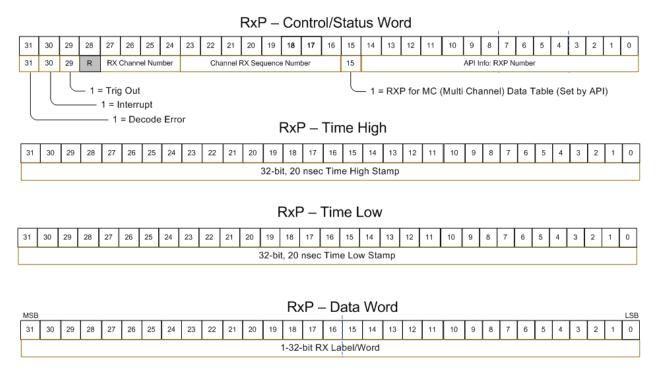

| RxP: Receive Packet Data Structure                            | 73 |

| Figure RX-3: Receive Packet (RxP)                             | 73 |

| RxP Control/Status1: W: 0x0000                                | 73 |

| Bits 0-15: API Info RXP Number                                | 73 |

| Bits 16-23: API Info RXP Number                               | 73 |

| Bits 24-27: RX Channel Number                                 | 74 |

| Bit 29: Trigger Out: W                                        | 74 |

| Bit 30: Interrupt: W                                          | 74 |

| Bit 31: Decode Error                                          | 74 |

| RxP Time Stamp Words: 0x0004 & 0x0008                         | 74 |

| RxP Data Word                                                 | 74 |

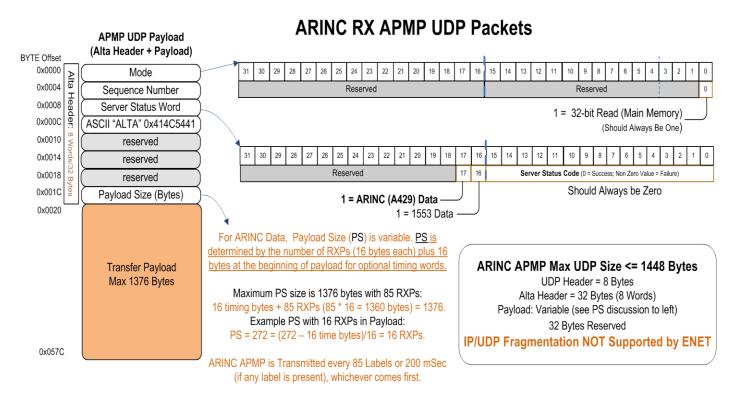

| ENET APMP UDP Format                                          | 75 |

| Figure RX-4: APMP UDP Packet Format                           | 75 |

| taCore-ARINC: Interrupt Functions                             | 77 |

| Interrupt Functions                                           | 77 |

| Figure Int-1: Interrupt Data Structures                       | 77 |

| Root Starting Interrupt Queue Packet (IQP) Address: W: 0x0100 | 78 |

| Root Current IQP Address: 0x0104                              | 78 |

| Root Interrupt Sequence Number: W: 0x0108                     | 78 |

| API – Reserved: 0x010C                                        | 78 |

| API – Reserved: 0x0110                                        | 78 |

| API – IQP Tail Pointer: 0x012C                                | 78 |

| Interrupt Queue Packets (IQP) – Extended Memory               | 78 |

| IQP Head Pointer: W: 0x0000                                   | 79 |

|   | Interrupt Type (16 Bits)   Interrupt Sequence Number (8 Bits)   Channel # (Number 8 Bits) : 0x0004 |      |

|---|----------------------------------------------------------------------------------------------------|------|

|   | ·                                                                                                  |      |

|   | Bits 0-7: Sequence Number                                                                          | 79   |

|   | Bits 8-15: Channel # (Number)                                                                      | . 79 |

|   | Bit 16: SG Interrupt (SGCB PTR)                                                                    | . 79 |

|   | Bit 20: BIT Fail Interrupt (BIT Status)                                                            | . 79 |

|   | Bit 21: Interval Timer                                                                             | . 79 |

|   | Bit 25: TX TxP Complete Interrupt (TX-CB Pointer)                                                  | . 80 |

|   | Bit 27: TX Stop Interrupt (TX-CB Pointer)                                                          | . 80 |

|   | Bit 28: TxP Complete Interrupt (TxP Pointer)                                                       | . 80 |

|   | Bit 29: RxP Multi Channel Interrupt (RxP Pointer)                                                  | . 80 |

|   | Bit 30: RxP CH Interrupt (RxP Pointer)                                                             | . 80 |

|   | Bit 31: RxP CH Mask Interrupt (RxP Pointer)                                                        | . 80 |

|   | Data Structure Pointer: W: 0x0008                                                                  | . 80 |

| R | evision Information                                                                                | 81   |

|   |                                                                                                    |      |

<~~~>

#### AltaCore-ARINC™

# **Document Introduction**

#### Introduction

This document is the Specifications-User's Manual Document for Alta Data Technologies' (ADT) *AltaCore-ARINC* protocol engine (PE), which supports various ARINC communications (usually based on ARINC-429 physical layer). This document specifies the design of the product and provides an overview for the reader who wants a detailed understanding of the *AltaCore-ARINC* design. The reader should also reference the *AltaAPI* manual (found on the CD or Alta web site) and source code for detailed descriptions of the software/backplane interface to *AltaCore-ARINC*.

**NOTE:** For most customer applications, the PE's design and processes are transparent to the application as the *AltaAPI* manages PE setup and execution. Most customers can skip this entire manual and simply refer to the *AltaAPI* manual and example programs for their ARINC application requirements. It is also recommended that the reader review *AltaView* products to learn about advanced avionics products.

This document is divided into sections that describe the major data structures of the *AltaCore-ARINC* PE:

- Introduction (This Section)

- Global Registers (Card Level)

- PE Root Device Level Registers (Channel Bank Level)

- Transmit (TX) Data Control

- Signal Generator (SG)

- Playback (PB) Estimated Release 1 Sept 2008.

- Receive (RX) Communications

- Channel Level RX

- Multi Channel RX

- Interrupts (Int)

This Introduction section provides an overview of the *AltaCore-ARINC* architecture and should be reviewed before reading the various data structure sections.

# **Terminology**

- This manual assumes the reader is very familiar with the general communications standards such as ARINC-419/429/573/575/717 and RS-232/422/485 style communications.

- msec = milli seconds; μsec = micro seconds; ηsec = nano seconds.

- An Alta card/board can contain one or more devices. A device is 16 channels (RX/TX configuration will vary). Another term for device is bank.

- Device = Bank (This is group of ARINC 16 or less channels).

- When discussing "Global" registers or values, these apply to ALL devices.

- The term "ROOT" register or value is for a specific device.

## AltaCore-ARINC Architecture and Document Basics

*AltaCore-ARINC* is a 32-bit based PE that can support up to 16 ARINC channels (a "device" or "bank of channels"). Many Alta cards have one or two banks per card. The pure FPGA 32-bit design greatly enhances backplane/processor throughput as compared to other older 16-bit interfaces.

# **Memory Mapped Architecture**

The *AltaCore-ARINC* protocol engine (PE) utilizes dedicated on-chip (FPGA on-chip memory) and/or on-board Extended Memory (depending on the PE configuration).

The memory of the PE/Card appears as a contiguous memory map to the host backplane regardless of the on-chip or on-board configuration (additional PE FPGA logic provides the arbitration for host access and various PE channel access). For most Alta card designs, an *AltaCore-ARINC* product uses high speed Quad Data Rate RAM or ZBT RAM, but the design is flexible and can be integrated to most common RAM channel architectures.

The *AltaAPI* or customer's application addresses each RX or TX channel through memory offset or software pointer schemes. The *AltaAPI* user/API's manual provides details of host driver and memory mapping requirements. Your Alta Product Hardware Manual (on the CD or the Alta web site download) details the memory configuration for your product (most card level products have one mega bytes of dedicated on-board memory per 16 channel bank), pin-outs and special configurations. Figure Intro-1 shows the basic memory mapping configuration for a single bank of 16 RX/TX channels. Special configurations may vary.

# AltaCore-ARINC Memory Map (Boards with One Megabyte Partitions) BYTE offset 0x000000 Global HW/FPGA Registers One Megabyte 0x100000 16 Channels 1Mbytes Bank1 0x200000 16 Channels 1Mbytes 5 Megabytes Bank2 Total Memory 0x300000 Reserved 0x400000 Reserved

Figure Intro-1: Basic *AltaCore-ARINC* Memory Map

# **Global Registers**

Global Registers are settings and values for ALL devices. These controls are usually for card-level functions and are not necessarily tied to a channel. When *AltaCore-ARINC* is sold as embedded IP, the device may NOT include Global Functions (this is specified at time of quote/order).

# RX and TX Buffer and Interrupt Data Structures: Root verses Extended Memory

RX and TX functions have two levels of data structures that control execution: Root Registers and Extended Memory Data Structures that direct sub-functions and provide data buffering. Root Registers reside in the FPGA on-chip memory and have fixed address offsets absolute to the card's and channel's base address. Extended Memory Pointer Tables and Buffers have relative addresses whose base (root) values are set in the Root Registers. Each major Root or Extended Memory function typically has Control, Status (CSR's) or Setup Registers that provide setup options (control) and execution feedback (status).

All options and data structures are detailed in the following manual sections.

**NOTE:** Several data structures of the PE are pointers to other tables or buffer data structures. The user/API must take great care to never populate a utilized structure with a null pointer or improper value (a value outside the on-board memory range). For example, if an RX Channel is turned-on and the Root or secondary pointer arrays are not properly programmed, then the PE will have unpredictable results (like any design that has a bad pointer reference). The PE

will not check for null or improper values and bad pointers will cause unpredictable behavior. The *AltaAPI* properly manages and provides allocation/destruction functions for the user/API application.

# **Memory Offset References**

Memory references in this document are in byte offsets. The PE memory (a common word) is 32-bit atomic machine, 4-byte aligned.

#### **Packed Word and Bit Data Structures**

AltaCore-ARINC data structures are typically packed 32-bit word structures that may have embedded bit fields or single bit settings. The right most bit is LSB bit 0 (zero) and the left most bit is MSB 31. The general rule is that a bit value of 1 (one) is an "on/set/positive" and a 0 (zero) is "off/clear/negative."

All data structures will be labeled "**W**" (Write) if the user/API's application (or **AltaAPI**) has the capability to write the value of the respective data element (word, bit or packed bits). Unless noted in the description, assume all data structures may be read by the user/API's application. The safest way to set control bits is to read the respective register using an OR (to set) or AND (to clear) in the selected bits and then write back. Great care must be taken to not set or change values of active registers during execution.

# **Execution Times, Channel Timing, Time Tags**

Execution times provided herein are respective to the PE and do not include backplane transfer times. In general, after execution of a transmit function, the user/API should allow 20  $\mu$ secs settling time (process overhead) for accurate future transmission timing (for example, the user/API needs to provide 20  $\mu$ secs of non activity at the end of a TX minor frame to assure accurate Minor Frame/Minor Frame timing to 20  $\mu$ secs). There are some special cases that require more than 20  $\mu$ secs and the reader should reference the respective section for detailed timing requirements.

The user/API will have several options for programming gaps (idle/dead time between words or label/word lists). These values are typically 32-bit, 100 nsec tick values.

#### **Reserve Bits and Words**

Many bits and words are "Reserved" for future use or are used by the PE execution. All Reserved BITS should assume a value of zero. Reserved Words/Bits values should not be changed and in most cases should default to zero. If a reserved word is part of a larger data structure word packet, assume a value of zero for initialization, but then do not write to this word. For updating packed bit-word structures, the user/API's application should first read the word and then logically OR-in the desired one bits (or AND-out the zero bits) and then write back to the same location (please see the *AltaAPI* source for

numerous examples). The API source code is provided and illustrates the proper set and rules for memory access – for custom applications, please use the API as a design guide.

# **Figure Color Codes**

In the following figures, a brown outline/white box signifies a bit/word/area that is programmed by the user/API. The light gray is usually a reserved bit/word/area and should not be changed by the user/API (the PE will update or use this element for processing). Most gray/reserved areas should be set to zero and most of these areas can be read by the user/API without affecting PE processing.

# AltaCore-ARINC Global Registers (Card Level)

# **Global Card Level Registers**

The area that occupies the first megabyte of the card memory map contains backplane and global card level settings and status values that affect processing for all devices. This area also contains the digital discrete, time and Built-In-Test (BIT) values of the card.

# Global Hardware (PE) Setup/Control/Int Registers

Figure Global Registers-1: Global Card Level Registers

# HW/Backplane CTL Registers (16 words - 0x00000000-0000000F)

The first 16 words of the memory map are reserved for backplane configuration registers. Please see your product's Hardware Manual for details on these registers.

# **Global Registers**

<sup>\*</sup>Note: For most 1553 cards, the number of input and output triggers is equal to the number of channels on the board. ARINC (ARINC typically have only one trigger per bank. See your hardware manual for details on triggers/pin-outs available for your configuration.

# Figure Global Registers-2: Device Global Registers

# Global Registers

(continued)

\*Note: The number of single-ended and differential discretes varies from board to board. See individual board HW manuals for details on discrete counts.

Figure Global Registers-2A: Device Global Registers

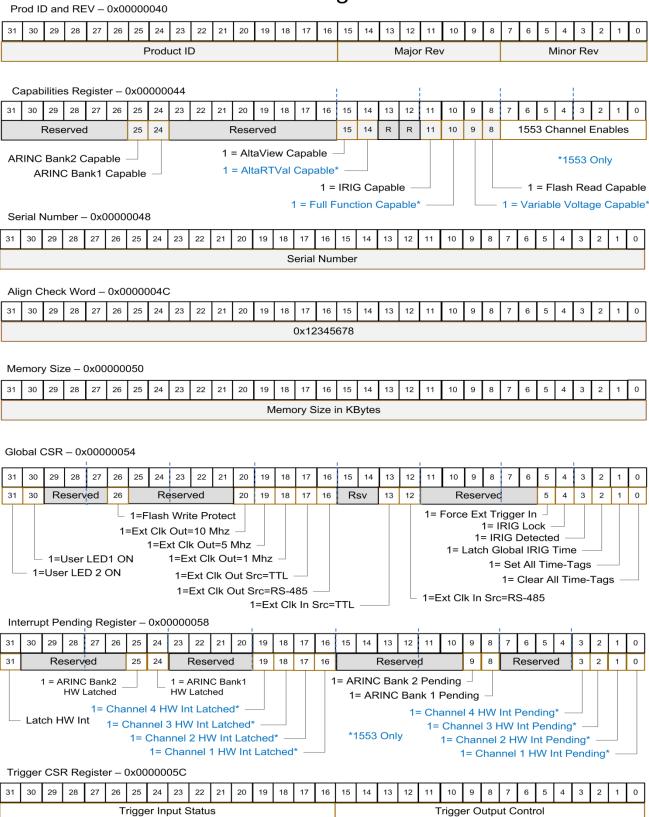

# Product ID and Rev: 0x00000040

This register provides the *AltaCore-ARINC*/FPGA Program ID and Revision.

# Capabilities Register: 0x00000044

This register provides settings for product options and capabilities. This allows Alta software to verify purchased or configured configuration.

**NOTE**: \*These Bits Apply to 1553 Channels Only. These should be treated as reserve for ARINC only cards.

#### Bits 0-5: 1553 Channel Enables\*

The channel enable bits indicate which channels are enabled on the board. For instance, if a two channel board was purchased, Bits 0 and 1 should be set to indicate that Channels 1 and 2 are enabled. (1553 Cards Only)

#### Bit 8: Flash Read Capable

This bit is set to a one if the Flash Read option is enabled on the board. This option enables the user/API to program setup data into on board flash. On power-up or reset, the setup data is copied from Flash to PE memory space. For more information regarding this feature, please contact Alta.

# Bit 9: Variable Voltage Capable\*

This bit is set to a one if the Variable Volt option is enabled on the board.

# Bit 10: Multi-Function Capable\*

This bit is set to one if the Multi-Function option is enabled on the board. When the Multi-Function bit is set to a one, TX, RT, and BM functions can be run simultaneously. When this bit is zero, the PE is operating in Dual-Function mode where only TX/BM or RT/BM functions can run simultaneously. For example, TX and RT functions cannot be enabled at the same time.

#### Bit 11: IRIG Capable

This bit is set to one if IRIG capability is enabled on the board.

# Bit 14: AltaRTVal Capable\*

This bit is set to one if *AltaRTVal* capability is enabled on the board. This option must be purchased on a board-by-board basis to allow *AltaRTVal* software to run with the board. (1553 Cards Only)

## Bit 15: AltaView Capable

This bit is set to one if FULL *AltaView* capability is enabled on the board. This option must be purchased on a board-by-board basis to allow *AltaView* software to run with the board.

#### Bits 16-23: Reserved

# Bit 24: ARINC Bank1 Capable

This bit is set to one if the first device bank of ARINC channels is available. If this bit is set to one, then read Device-Level PE Root register 0x000C to determine the number of RX and TX channels for the device bank (different cards can have different RX/TX selection capability – see your card's Getting Started & Hardware Manuals for details).

#### Bit 25: ARINC Bank2 Capable

This bit is set to one if the second device bank of ARINC channels is available. If this bit is set to one, then read device-level PE Root register 0x000C to determine the number of RX and TX channels for the device bank (different cards can have different RX/TX selection capability – see your card's Getting Started & Hardware Manuals for details).

#### Bits 26-31: Reserved

#### Serial Number: 0x00000048

This register provides the Born on Date and Incremental Serial Number of the card (the two left most segments seen on the card label – "YYMM-NUMBER"). The 16 MSBs make-up 4 BCD nibbles that provide the YYMM (Y=Year, M=Month) digits. The 16 LSBs represent the serial number 65535/99999 value.

#### Alignment Test Register: 0x0000004C

This register provides a simple 1,2,3,4,5,6,7,8 value in each nibble (0x12345678 word) so that an operating system driver developer can check for proper word/byte alignment. Nibble bits 28-31 has the value 1 (one).

#### Memory Size: 0x00000050

This register tells the user/API the size in K bytes for the total card. Only the lower 16 bits are used and for most cards this should be a value of 0x00001400 (5120 Kbytes = 5 Mbytes).

#### Global CSR: W: 0x00000054

This word is provided for user/API applications that want to control all channel time tags and HW Interrupt enables from one location. All of these settings are duplicated at the channel level for multi applications. This is a packed bit structure whose bits are defined in the following paragraphs.

#### Bit 0: Clear All Time Tags: W

This bit is set to one by the user/API to direct the PE to clear/zero all channel time tags (PE Time High & Low clocks), which are utilized to time tag ARINC label/word

list (Receive Packets – RxPs). Time clearing occurs  $<1\mu$ sec from this bit being set. This bit is self clearing.

#### Bit 1: Set all Time Tags: W

This bit is set to one by the user/API to direct the PE to load all local PE Time High & Low registers (offset 0x0024/28) at the same time (with the user/API loaded values). This allows all channels to have their clocks jammed with user/API time simultaneously. Otherwise, the user/API application would need to perform this bit setting for each PE channel and time values would be skewed. Time loading occurs <1µsec from this bit being set. This bit is self clearing.

#### Bit 2: Latch Global IRIG Time: W

This bit is set to a one by the user/API to load the current IRIG time into the IRIG Time Global Registers (offsets 0x00C8/CC). This bit is self clearing.

#### Bit 3: IRIG Detected: R

This read only bit set to a one indicates that activity has been detected on the IRIG input signal. Once activity has been detected this bit will remain set until no activity has been detected for 5 seconds. This bit does not mean IRIG lock has occurred (see bit 4 below), it is simply an indicator that "something" has been detected on the input signal within the last 5 seconds.

#### Bit 4: IRIG Lock: R

This read only bit set to a one indicates that the IRIG decoder has locked on a good IRIG signal. To achieve IRIG Lock the IRIG decoder must detect at least one valid IRIG time frame. IRIG Lock will be lost if at any point the IRIG decoder detects an invalid time frame. Once IRIG Lock is lost this bit will get set to zero and the IRIG decoder will go into search mode looking for another valid IRIG time frame.

#### Bit 5: Force Ext Trigger In: W

This bit set to a one by the user/API forces an input trigger to all channels simultaneously. Setting this bit overrides the external trigger signal on each channel. This bit provides the means for a software trigger as opposed to and external HW trigger. This bit is self-clearing.

For example, the user/API can setup the TX on each channel to wait for an external input trigger. Once the TXs are setup, enabled and waiting for a trigger, this bit can be set to start all TXs simultaneously.

#### Bits 6-11: Reserved

#### Bit 12: Ext Clk In Src=RS-485: W

Setting this bit to a one will select the differential "DDISC1" RS-485 lines as the external clock input. See the individual board HW manual for pin assignment for the DDISC1 (+) and (-) signals.

#### Bit 13: Ext Clk In Src=TTL: W

Setting this bit to a one will select the differential Ext TTL Clock line as the external clock input. See the individual board HW manual for pin assignment for the External TTL Clock I/O Signal.

#### Bits 14-15: Reserved

#### Bit 16: Ext Clk Out Src=RS-485: W

Setting this bit to a one will select the differential "DDISC1" RS-485 lines as the external clock output. See the individual board HW manual for pin assignment for the DDISC1 (+) and (-) signals.

**NOTE:** If the RS-485 option is used for the external clock, the input and output clocks use the SAME PINS. Therefore, the input clock for all channels on the board are automatically connected to the output clock, so you can test the external clock on those channels without any external connection. Of course, if you need to synchronize with other boards then one board should be configured to output a clock signal and connected to the appropriate external clock input lines on the other boards (which are configured to accept the external clock signal and will NOT generate an output clock).

# Bit 17: Ext Clk Out Src=TTL: W

Setting this bit to a one will select the differential Ext TTL Clock line as the external clock output. See the individual board HW manual for pin assignment for the External TTL Clock I/O Signal.

**NOTE:** If the Ext TTL Clock option is used for the external clock, the input and output clocks use the SAME PIN. Therefore, the input clock for all channels on the board are automatically connected to the output clock, so you can test the external clock on those channels without any external connection. Of course, if you need to synchronize with other boards then one board should be configured to output a clock signal and connected to the appropriate external clock input lines on the other boards (which are configured to accept the external clock signal and will NOT generate an output clock).

Bit 18: Ext Clk Out=1 MHz: W

Setting this bit to a one will set the Ext Clock output frequency to 1 MHz.

Bit 19: Ext Clk Out=5 MHz: W

Setting this bit to a one will set the Ext Clock output frequency to 5 MHz.

Bit 20: Ext Clk Out=10 MHz: W

Setting this bit to a one will set the Ext Clock output frequency to 10 MHz.

Bits 21-25: Reserved

Bit 26: Flash Write Protect: R

If this bit is set to a one all non-volatile memory on board will not be writable. Generally this means the board was ordered with a –N option.

Bits 26-29: Reserved

Bit 30: user/API LED1: W

Setting this bit to a one will turn on user/API Led1. See the individual board HW manual for user/API LED1 locations.

Bit 31: user/API LED2: W

Setting this bit to a one will turn on user/API Led2. See the individual board HW manual for user/API LED2 locations.

# Summary of Multi Application verses Single Application Interrupt Options with AltaCore-ARINC

**Multi Applications Scenarios:** (usually one application per device for interrupts): All Interrupt signals are handled at the PE device level. You only need to read the next section and the Interrupt Section for details.

Single Application Scenarios: You have a choice to handle interrupt management at the device level or handle interrupt pending at the global level, which is why the following word and bits are provided. If you want to handle interrupts strictly at the device level, then treat this as a multi application scenario. If you want to handle interrupt pending signals at a single card/global level (which may save time on host reads/writes), then read the following paragraphs and the Interrupt Section of this manual for this supported option.

# Global Interrupt Register: W: 0x00000058

This register is provided for applications that want to control all device interrupt hardware actions from one location verses managing each PE device individually (multi application processes would need to manage each device as an independent, logical device). These bits are duplicated at the PE device level. This is a packed bit structure whose bit values

are defined in the following paragraphs. A brief discussion follows to provide the general overview of the bit values and proper execution action of reading the bits.

This register provides a pending and latching bit value for each of the ARINC channel devices. Bit 31 can be set to a one by the user/API to "latch" active interrupt signals and immediately clear the cards channel/bank interrupt pending signal to the host backplane/system (all channel/bank interrupt pending signals, or bits, are OR'ed together to set the backplane interrupt pending signal). So bit 31 provides the application a single bit to clear the card's interrupt pending bit to not hold-off other possible interrupt pending conditions in the system (from other cards). This would not be multi application safe as independent application would need to service their respective channel/bank: there is a mechanism to clear interrupt pending at the channel/bank level, too.

In the PE Root Control Word (channel level), there is a "Hardware (HW) Interrupt On" bit that controls the interrupt pending condition to drive the card level backplane/system interrupt hardware line. Please see PE Root Registers – Control and Status Word for channel level interrupt settings.

#### Bits 0-3: Interrupt Pending

These bits, one per 1553 PE channel or ARINC device bank, are set to a one by the PE when an interrupt event(s) has posted for the respective channel/bank (please see the diagram for the channel mapping). When an interrupt has occurred (or when the host application conducts a polling event), the user/API application reads this register to see what channel/bank caused the interrupt. When the channel/bank level Interrupt Pending bit in the Root PE Status Word is cleared (set to zero), or when bit 31 of this word is set to one, then the respective pending bit is cleared (and if the hardware interrupt is turned on, then the backplane/system, interrupt pending signal is cleared). The user/API does not clear these bits to clear an interrupt signal.

#### Bits 4-15: Reserved

#### Bits 16-19: Interrupt Latched: W

These bits are provided as a copy of the pending bits in this word when the hardware interrupt signal is cleared (from writing a one to bit 31). After the user/API interrupt service routine has written a one to bit 31, these bits hold the current value of the pending bits (please see the diagram for the bit position for respective channel/bank). This allows user/API applications that want to handle interrupts at the global level to quickly clear the hardware event from the backplane/system and then read these bits to see which channel/bank caused the interrupt. The user/API application should clear these respective bits for the next

interrupt event handler. Multi application processes would read interrupt pending events only at the PE Channel/Bank Level (described above).

# Bits 20-30: Reserved

#### Bit 31: Latch Hardware Int: W

This self clearing bit is set to one by the user/API to direct the PE to clear the hardware interrupt pending signal to the backplane/system, clear the interrupt pending bits in this word and copy their value to the interrupt latch bits in this word (all action described in the previous paragraphs). Software polling interrupt event handlers do not touch this bit.

# Trigger CSR: W: 0x0000005C

This word is provided for user/API applications that want to know the state of the input triggers and is also used to override the output triggers. Normally the output triggers are controlled by the PE when the "generate output trigger" bit is set in a PE control register. The number of input and output triggers is equal to the number of channels on the board.

## Bit 15-0: Trigger Output Control: W

Trigger outputs can be driven low (Active) by setting the corresponding bit in this register to a one. Bit0=Trigger1, Bit1=Trigger 2, etc.

# Bit 31-16: Trigger Input Status:

These bits show the status of the input triggers. A one for a given bit indicates that the trigger is in-active and a zero indicates the trigger is active. Bit16=Trigger1, Bit18=Trigger 2, etc.

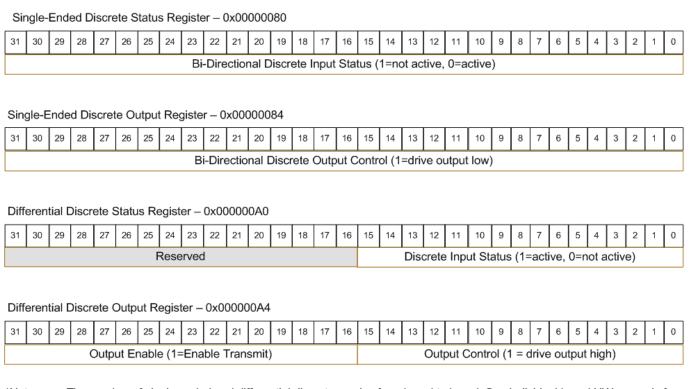

# **Discrete Configurations – See Product Hardware Manual**

See your product's Hardware Manual for Discrete Configuration and Pin-Outs. Most ARINC cards have limited discrete configurations (usually only 1-8).

#### Single-Ended Discrete Status Register: 0x00000080

This word shows the input status of the bi-directional avionics discretes. A one for a given bit indicates that the discrete is in-active and a zero indicates the discrete is active. Bit0=Discrete1, Bit1= Discrete2, etc.

NOTE: The input voltage should not exceed 30 Volts. Exceeding this rating can damage the board.

# Single-Ended Discrete Output Register: W: 0x00000084

This word is used to control the output state of the bi-directional avionics discretes. Discrete outputs can be driven low (Active) by setting the corresponding bit in this register to a one. Bit0=Discrete1, Bit1= Discrete2, etc.

NOTE: The bi-directional Avionics Discretes can sink up to 1 Amp when active. Exceeding this rating can damage the board.

# **Differential Discrete Status Register: 0x000000A0**

This word shows the input status of the differential RS485 discretes. A one for a given bit indicates that the discrete is active and a zero indicates the discrete is inactive. Bit0=Discrete1, Bit1= Discrete2, etc.

# Differential Discrete Output Register: W: 0x000000A4

This word is used to control the output state of the differential RS485 discretes.

#### Bit 15-0: Output Control: W

Discrete outputs can be driven high (Active) by setting the corresponding bit in this register to a one. Bit0=Discrete1, Bit1= Discrete2, etc. The corresponding transmit enable bit must be set before this bit is valid. Bit0=Discrete1, Bit1= Discrete2, etc.

# Bit 31-16: Output Enable: W

These bits control the output enables of the uni-directional differential RS485. If a given bit is set to a one, the discrete output is enabled (transmit mode). If a given bit is set to a zero, the discrete output is disabled (receive mode). Bit16=Discrete1, Bit17= Discrete2, etc.

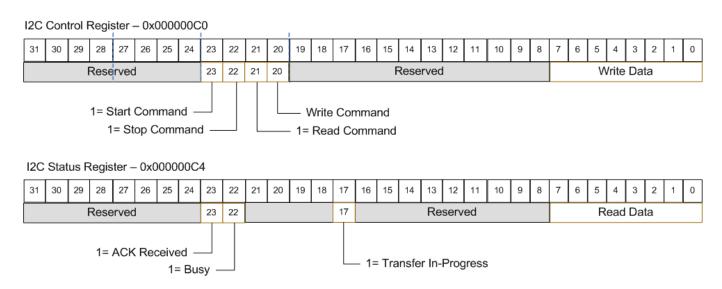

# I2C Control Register: W: 0x000000C0

This word is used to control the I2C logic on the board. See the individual board HW manual for more details on this register. The user/API's application does not need to know details of this register – the *AltaAPI* handles all overhead and management of these registers – please see source code of *AltaAPI* for details.

# I2C Status Register: 0x000000C4

This word provides the status of the I2C logic on the board. See the individual board HW manual for more details on this register. The user/API's application does not need to know details of this register – the *AltaAPI* handles all overhead and management of these registers – please see source code of *AltaAPI* for details.

# IRIG Time High: 0x000000C8

This word shows current IRIG Time High value. To latch the current IRIG time in this word, the Latch IRIG Time (Bit 2) in the Global CSR should be set prior to reading this word.

#### IRIG Time Low: 0x000000CC

This word shows current IRIG Time Low value. To latch the current IRIG time in this word, the Latch IRIG Time (Bit 2) in the Global CSR should be set prior to reading this word.

**NOTE:** The IRIG times latched in the registers described above are one second behind. The user/API's code will need to adjust the time +1 second. Check your AltaAPI release notes for this +1 second adjust made to the IRIG read function.

#### **IRIG Code Formats**

Alta IRIG receive capability supports the following formats.

- IRIG-B002, Format B, DC Level Shift, no index count interval, BCDTOY

- IRIG-B122, Format B, Amplitude Modulated, 1khz Carrier, BCDTOY

- IRIG-B006, Format B, DC Level Shift, no index count interval, BCDTOY, BCDYEAR

- IRIG-B126, Format B, Amplitude Modulated, 1khz Carrier, BCDTOY, BCDYEAR

# PTP IEEE-1588 Registers: 0x0100-0x010C

These 4 registers are for ENET/ENET2 devices for key PTP IEEE-1588 Time Sync and Control-Status (CSR) registers. ENET devices can synchronize time via 1588 grand masters in a similar manner to IRIG synchronization. If engaged (via user software API settings), this overrides IRIG sync decoding.

For details on implementation, please contact Alta for access to the PTP IEEE-1588 Design Implementation Application Note and reference the appropriate sample C programs. Contact Alta at <a href="mailto:alta.support@altadt.com">alta.support@altadt.com</a> or 888-429-1553 x2.

<~~~>

# AltaCore-ARINC: Root PE Device/Bank Registers

#### Introduction

There are several control and status settings at the device level for ARINC functions and events. The following figure provides an overview of the Root registers memory map. This section will describe the Root PE Registers that are common for ARINC channels functions of the respective device (bank of channels). The subsequent sections of manual will detail the Root Registers for the respective RX, TX, Interrupt functions (as shown in the figure below).

Figure PE Root-1: Root ARINC PE Device Memory Map

Each of the major Root Register areas shown above are detailed in their respective sections of this manual. This section will now detail the Root PE Registers (0x0000-0x00FF) that affect top-level for all device (channel) functions. The following figure and paragraphs details this area.

#### ARINC Root PE Registers BYTE offset Root PE Registers 26 25 24 23 22 21 20 19 18 17 0x0000 PE Control SG CH Num 0x0004 PE Status INTVL ON 1 = PB Time Set 0x0008 PE ID and Version 1=APMP 1 = PB Time Read 1 = Ext Input Clk=10Mhz 0x000C TX\RX Channel Enables 1=APMP On 1 = Ext Input Clk=5Mhz 0x0010 1= Skip PB With Reserved 1 = Ext Input Clk=1Mhz Time Back-up 1 = Use External Clk 0x0014 Total RxPs Received 1= Do Not Reset PB 1 = Read Time-Tag Clock at Start 0x0018 Total TxPs Transmitted 1= PB ON 1 = Set Time-Tag 1 = INT on BIT Fail 1 = Zero Time-Tag 0x001C PE Time High 1= Trig In: Low to High 1 = Read IRIG Time 1 = Run Initiated BIT 0x0020 PE Time Low 1 = Channel Reset 1 = Force Ext Trigger Out 0x0024 1 = Force Ext Trigger In IRIG Time High 1 = Clk Trig Enable 0x0028 IRIG Time Low 1 = Signal Generator Mode On -0x002C **BIT Status** 0x0030 API - Channel In Use 1 = HW Interrupt On 0x0034 Signal Capture CSR CH 1 0x0038 Signal Capture Data CH 1 0x003C Signal Capture CSR CH 2 1 = Interrupt Pending 1 = Flash Read Enabled 1 = Signal Capture Enabled 0x0040 1 = IRIG Detected Signal Capture Data CH 2 1 = IRIG Lock 0x0044 Reserved 26 25 24 23 22 21 0x0080 Multi Channel RxP Pointer Bank TX Enables (Bit 16 = TX0) Bank RX Enables (Bit 0 = RX0) 0x0084 The number of Tx and Rx Channels Varies Depending on Order Configuration - See Your Getting Started and Hardware Reserved Manual for Details on Configurations and Pin-Outs 0x008C 0x00C0 15 PTP 1588 Reserved Registers 0x00F8 0x00FC Reserved 1 = POST BIT Failure 1 = Periodic BIT Failure = Initiated BIT Failure 1 = Time-Tag Test Failure 1 = POST BIT In-Progress 1 = Processor Test Failure 1 = Memory Test Failure 1 = Periodic BIT In-Progress 1 = Initiated BIT In-Progress

Figure PE Root-2: Root PE Registers

## **Root PE Control Word: W: 0x0000**

This register is a packed bit structure and provides key PE control for the user/API. The following paragraphs detail the bit settings.

#### Bit 0: HW Interrupt On: W

This bit is set to a one by the user/API to direct the PE to enable hardware interrupts to the backplane (or interrupt line of an FPGA core build). Interrupt events from RX or TX Channels are logged in the Interrupt Queue regardless of this setting (see the respective section for details). Setting this bit to zero requires the user/API's host application to poll the interrupt queue to service

events. Setting this to a one will require the user/API's host application to have an operating system interrupt service routine (ISR) to handle the backplane interrupt and then read the Interrupt Queue to service the events.

## Bit 4: Signal Generator Mode On: W

This bit is set to a one by the user/API to direct the PE to start the Signal Generator (see the Signal Generator (SG) section of this document for details. Normal channel TX or PB cannot be operating during SG mode.

# Bit 5: Clock (CLK) Trigger Enable: W

This bit is set to one by the user/API to direct the PE to NOT increment the RX Time Tag (PE Device) clock or the Playback control clock until an external trigger has been detected. This allows the user to jam all the appropriate device RxP time tag clocks and playback clocks with a system value and then have an external trigger synchronize the starting of the clocks (either incrementing off the PE's internal 50 MHz clock or an external 1, 5 or 10 MHz clock).

#### Bit 6: Force External Trigger In: W

This bit is set by the user/API to direct the PE to set external triggers for all devices and any of their PE functions that may be stalled for ext trigger (for example the user/API can set Wait for Ext Trigger on TX and BM). This bit is extremely useful to ensure all TXs start within 5 µsecs of each other. Most competitive products require software control of each channel resulting in huge delays between channels. This bit is self clearing.

# Bit 7: Force External Trigger Out: W

This bit is set by the user/API to direct the PE to override its output trigger. Normally the output trigger is controlled by the PE when the "generate output trigger" bit is set in a PE control register. This bit allows a software application to generate an output trigger on demand. This bit is self clearing.

#### Bit 8: Read IRIG Time

This bit is set to a one by the user/API to direct the PE to latch (for reading) the PE's internal 64-bit, 20 nsec time and the most current IRIG Time High & Low values to the Root PE Registers Time High & Low (offsets 0x001C/20) and IRIG Time & Low registers (offsets 0x0024/28). See IRIG Time High & Low Registers later in this section for more discussion on IRIG time. The latency is <1µsec. If IRIG Time is not being used, then the value in the IRIG time registers is unpredictable. This bit is self clearing.

**NOTE:** The IRIG times latched in the registers described above are one second behind. The user/API's code will need to adjust the time +1 second. Check your AltaAPI release notes for this +1 second adjust made to the IRIG read function.

# Time Tag Discussion (Time High & Low):

Each PE Channel has a 64-bit, 20 nsec internal timer that is used to time tag all label/word lists in all modes (Time High & Low in every Receive Packet, RxP, see the RX Section of this manual). The PE provides the user/API a 2-word (Root Time High & Low – Root PE Register offset 0x001C/20) window to access the internal PE timer. These Root Time High & Low registers are used to program or read the internal timer per the bit selections discussed in the ensuing paragraphs.

# Bit 9: Zero Time-Tag: W

This bit is set to a one by the user/API to direct the PE to zero/clear the PE Time High & Low registers (offsets 0x001C/20), which is used for time stamping label/words. The PE clears this bit when the clock registers have been set to zero.

#### Bit 10: Set Time-Tag: W

This bit is set to a one by the user/API to direct the PE to read the user/API written values in Time High & Low and jam/set the internal PE time registers (offsets 0x001C/20), which is used for time stamping RxP label/words. The PE will clear this bit when the read/jam is finished. The delay from this bit being set to the internal time tag register being jammed is <1µsec (latency). This bit is self clearing.

#### Bit 11: Read Time-Tag: W

This bit is set to a one by the user/API to direct the PE to latch the internal time to the PE Time High & Low registers (this allows the user/API to read the time values and is an excellent "heart beat" check on the PE – this is clock used for RXP time stamping). The latency is <1µsec. The PE will clear this bit when the time values have been written.

# Bit 12: Use External Signal:W

This bit is set to a one by the user/API to direct the PE to use the selected (RS-485 or TTL) external input to drive the clock count (PE Time High & Low).

# Bit 13: Ext Input Clk = 1 Mhz

Setting this bit to a one will indicate to the PE that the external input clock frequency is 1 MHz.

#### Bit 14: Ext Input Clk = 5 Mhz

Setting this bit to a one will indicate to the PE that the external input clock frequency is 5 MHz.

#### Bit 15: Ext Input Clk = 10 Mhz

Setting this bit to a one will indicate to the PE that the external input clock frequency is 10 MHz.

#### Bits 16-19: Reserved

#### Bit 20: PB Time Set: W

This bit is set to a one by the user/API to direct the PE to read the user/API written values in Time High & Low and jam/set the internal PE time registers (offsets 0x001C/20), which is used for PB (Plaback timer functions. The PE will clear this bit when the read/jam is finished. The delay from this bit being set to the internal time tag register being jammed is <1µsec (latency). This bit is self clearing.

#### Bit 21: PB Time Read: W

This bit is set to a one by the user/API to direct the PE to latch the internal time to the PE Time High & Low registers (this allows the user/API to read the time values and is an excellent "heart beat" check on the PE – this is clock used for PB transmission control). The latency is <1µsec. The PE will clear this bit when the time values have been written.

## Bit 22: Trigger In Low to High: W

This bit is set to one by the user/API to direct the PE to accept a Low to High (0 to 1 edge) trigger verses the default high to low edge trigger.

## Bit 23: PB On: W

This bit is set to one by the user/API to direct the PE to start PB transmission across all selected TX channels. The user must also set the TX channel PB On bit in the respective TX/PB CSR1 Word.

#### Bit 24: Do Not Reset PB Clock at Start: W

This bit is set to one by the user/API if the PE should NOT reset the playback internal clock at the start. This bit must be set for absolute timing. Usually, this user/API will have set/preset the PB internal clock with a desired value prior to starting PB (setting bit 0 to one).

## Bit 25: Skip PXPs with Time Back-up: W

This bit is set to one by the user/API if the PE should skip PXPs with a time value less than the PB internal clock.

#### Bit 26: ENET APMP On - ENET-A429 ONLY

This bit is set to one to direct the PE to enable Alta Passive Monitor Protocol (APMP) for Multi-Channel ARINC channels. APMP mode is a feature for ENET-A429 devices only and will provide automatic UDP bridging of ARINC RXP label/words. Only RX Channels that have multi-channel mode enable in their

respective Setup1 channel register will be have their RXPs added to the APMP payload.

## Bit 27: APMP IRIG On - ENET-A429 Only

This bit is set to one to direct the PE to insert PE and IRIG Time words in the first four words of the APMP payload. Please see the end of the RX Section and the IRIG bookmark: Root IRIG Time High & Low: 0x0024/28.

## Bit 28: APMP INTVL On – ENET-A429 Only

This bit is set to one to direct the PE to inset PE and Interval Time words in the first four words of the APMP payload. Please see the end of the RX Section and the bookmark: Root Interval Timer: 0x004C

#### Bit 29: INT on BIT Fail

This bit set to a one will cause an interrupt to be generated when a BIT failure is detected. Note that an interrupt will only get generated on each instance that bits 7-0 of the Bit Status Register (offset 0x002C) are set. For example, if a BIT Failure is detected multiple times, only one interrupt will get generated for that failure until the bit is set to zero by the user/API and another BIT Test failure is detected causing the bit to be set again. The user/API should clear the BIT status register once it has detected and processed the BIT failure.

#### Bit 30: Run Initiated BIT

This bit is set to a one by the user/API to direct the PE run Initiated BIT. This bit is self clearing.

#### Bit 31: Reset Channel

This bit is set to a one by the user/API to reset the PE channel. A channel reset will force all PE registers to a power-on state. For example, POST BIT will run, Time-Tag registers will get reset to zero, etc. This bit is self clearing.

NOTE: POST BIT performs a memory test which may cause some of the user/API data to be cleared. Once a channel reset performed, the contents of the PE registers and memory must be initialized again by the user/API.

## **Root PE Status Word: 0x0004**

This word provides the user/API status on four key indicators: Interrupt Pending for the Channel, IRIG Signal Detection. This is a packed bit structure whose values are detailed in the following paragraphs.

#### Bit 0: Interrupt Pending: W

This bit is set to a one by the PE to indicate that an interrupt event is pending in the channels interrupt queue. If the Root PE Control Word Bit 0, HW Interrupt On, is set to a one, then a backplane/system interrupt signal has been set. This

bit MUST BE cleared (set to zero) by the user/API to clear the backplane/system signal. Even if the HW Interrupt On bit is not on (so the user/API has decided against the channel being able to generate a backplane/system interrupt signal), the user/API should still clear this bit during an interrupt queue polling event so the bit can be utilized for the next interrupt event.

#### Bits 1-9: Reserved

#### Bit 10: IRIG Detected

This read only bit set to a one indicates that activity has been detected on the IRIG input signal. Once activity has been detected this bit will remain set until no activity has been detected for 5 seconds. This bit does not mean IRIG lock has occurred (see bit 11 below), it is simply an indicator that "something" has been detected on the input signal within the last 5 seconds.

#### Bit 11: IRIG Lock

This read only bit set to a one indicates that the IRIG decoder has locked on a good IRIG signal. To achieve IRIG Lock the IRIG decoder must detect at least one valid IRIG time frame. IRIG Lock will be lost if at any point the IRIG decoder detects an invalid time frame. Once IRIG Lock is lost this bit will get set to zero and the IRIG decoder will go into search mode looking for another valid IRIG time frame.

#### Bits 12-13: Reserved

#### Bits 16-20: Bit Time Tag

These bits contain the 5 least significant bits of the time-tag register and are used by the PE for Time-Tag BIT testing.

#### Bits 21-25: Reserved

#### Bit 26: Flash Read Enable