# AltaCore-1553™ MIL-STD-1553 Protocol Engine Specifications/User's Manual

Part Number: 14101-00000-H1 Cage Code: 4RK27 • NAICS: 334118

Alta Data Technologies LLC 4901 Rockaway Blvd, Building A Rio Rancho, NM 87124 USA (tel) 505-994-3111 • www.altadt.com

#### **Revision Control History**

Rev H1 Release Date: 18 October 2017

#### Note to the Reader and End-User:

This document is provided for information only and is © Alta Data Technologies LLC 2007-2017. While Alta strives to provide the most accurate information, there may be errors and omissions in this document. Alta disclaims all liability in document errors and any product usage. By using an Alta product, the customer or end user agrees (1) to accept Alta's Standard Terms and Conditions of Sale, Standard Warranty and Software License and (2) to not hold Alta Members, Employees, Contractors or Sales & Support Representatives responsible for any loss or legal liability, tangible or intangible, from any document errors or any product usage.

The product described in this document is not US ITAR controlled. Use of Alta products or documentation in violation of local usage, waste discard and export control rules, or in violation of US ITAR regulations, voids product warranty and shall not be supported. This document may be distributed to support government programs and projects. Third party person, company or consultant distribution is not allowed without Alta's written permission.

AltaCore, AltaCore-1553, AltaCore-ARINC, AltaAPI, AltaView and AltaRTVal are Trademarks of Alta Data Technologies LLC, Rio Rancho, New Mexico USA

#### Contact:

We welcome comments and suggestions. Please contact us at 888-429-1553 (toll free in US) or 505-994-3111 or visit our web site for support submit forms at www.altadt.com or email us at alta.info@altadt.com or alta.support@altadt.com.

## AltaCore-1553™

## **Table of Contents**

| AltaCore-1553™1                                                               |

|-------------------------------------------------------------------------------|

| Introduction1                                                                 |

| Terminology1                                                                  |

| AltaCore-1553 Architecture and Document Basics2                               |

| Memory Mapped Architecture2                                                   |

| Figure Intro-1: Basic AltaCore Memory Map3                                    |

| Root Data Structures                                                          |

| BC, RT, Monitor and Interrupt Data Structures: Control Blocks, CSRs and CDPs3 |

| Memory Offset References4                                                     |

| Packed Word and Bit Data Structures4                                          |

| Execution Times, Bus Timing, Time Tags4                                       |

| Reserve Bits and Words5                                                       |

| Figure Color Codes5                                                           |

| AltaCore-1553 Global Card Level Registers6                                    |

| Global Card Level Registers6                                                  |

| HW/Backplane CTL Registers (16 words - 0x00000000-0000000F)6                  |

| Figure Global Registers-2: User Global Registers8                             |

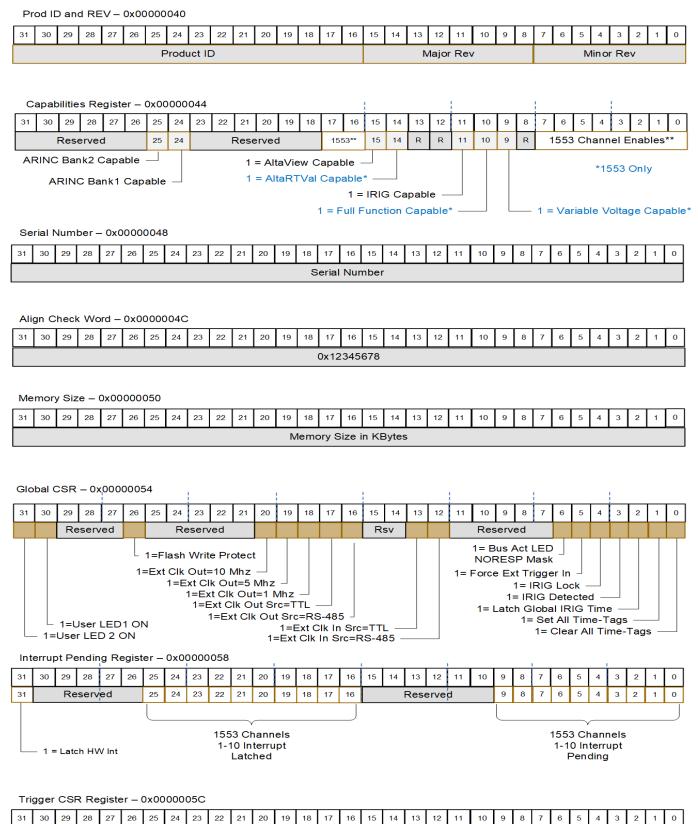

| Product ID and Rev: 0x000000409                                               |

| Capabilities Register: 0x000000449                                            |

| Bits 0-7, 16-17: 1553 Channel Enables9                                        |

| Bit 9: Variable Voltage Capable9                                              |

| Bit 10: Multi-Function Capable9                                               |

| Bit 11: IRIG Capable9                                                         |

| Bit 14: AltaRTVal Capable9                                                    |

| Bit 15: AltaView Capable9                                                     |

| Serial Number: 0x0000004810                                                   |

| Alignment Test Register                                                       |

| Memory Size: 0x00000050 10                                                    |

| Global CSR: W: 0x0000005410                                                   |

| Bit 0: Clear All Time Tags: W10                                               | ) |

|-------------------------------------------------------------------------------|---|

| Bit 1: Set all Time Tags: W10                                                 | ) |

| Bit 2: Latch Global IRIG Time: W10                                            | ) |

| Bit 3: IRIG Detected: R10                                                     | ) |

| Bit 4: IRIG Lock: R                                                           | l |

| Bit 5: Force Ext Trigger In: W11                                              | l |

| Bit 6: Bus Activity LED No Response (NORESP) Mask: W11                        | I |

| Bit 12: Ext Clk In Src=RS-485: W11                                            | l |

| Bit 13: Ext Clk In Src=TTL: W11                                               | I |

| Bit 16: Ext Clk Out Src=RS-485: W12                                           | 2 |

| Bit 17: Ext Clk Out Src=TTL: W12                                              | 2 |

| Bit 18: Ext Clk Out=1 MHz: W 12                                               | 2 |

| Bit 19: Ext Clk Out=5 MHz: W12                                                | 2 |

| Bit 20: Ext Clk Out=10 MHz: W                                                 | 2 |

| Bit 26: Flash Write Protect: R13                                              | 3 |

| Bit 30: User LED1: W 13                                                       | 3 |

| Bit 31: User LED2: W 13                                                       | 3 |

| Summary of Multi-application verses Single Application Interrupt Options with |   |

| AltaCore                                                                      | 3 |

| Multi Applications Scenarios:13                                               |   |

| Single Application Scenarios:                                                 | 3 |

| Global Interrupt Register: W: 0x000005813                                     | 3 |

| Bits 0-9: Interrupt Pending14                                                 | ł |

| Bits 16-25: Interrupt Latched: W14                                            | 1 |

| Bit 31: Latch Hardware Int: W15                                               | 5 |

| Trigger CSR: W: 0x0000005C 15                                                 | 5 |

| Bit 15-0: Trigger Output Control: W15                                         | 5 |

| Bit 31-16: Trigger Input Status:                                              | 5 |

| Discrete Configurations - README                                              | 5 |

| Single-Ended Discrete (SDISC) Status Register: 0x0000008015                   | 5 |

| Single-Ended Discrete Output Register: W: 0x000008416                         | 3 |

| Differential Discrete (DDISC)Status Register: 0x000000A0    |    |

|-------------------------------------------------------------|----|

| Differential Discrete Output Register: W: 0x000000A4        | 16 |

| Bit 15-0: Output Control: W                                 | 16 |

| Bit 31-16: Output Enable: W                                 | 16 |

| I2C Control Register: W: 0x00000C0                          |    |

| I2C Status Register: 0x00000C4                              | 16 |

| IRIG Time High: 0x000000C8                                  | 17 |

| IRIG Time Low: 0x000000CC                                   | 17 |

| IRIG Code Formats                                           | 17 |

| PTP IEEE-1588 Registers: 0x0100-0x010C                      |    |

| AltaCore-1553 Root PE Channel Registers                     |    |

| Introduction                                                |    |

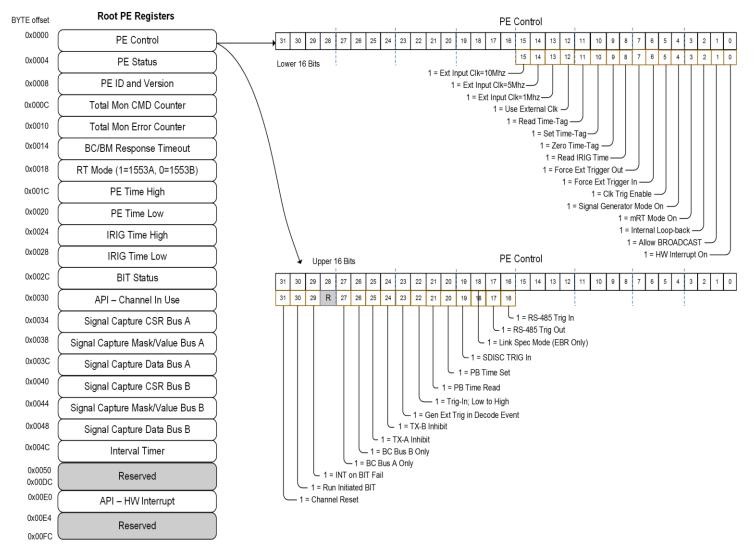

| Figure PE Root-1: Root PE Registers (per Channel)           |    |

| Figure Root PE-2: Root PE Registers: Control Word Break-Out |    |

| Root PE Control Word: W: 0x0000                             |    |

| Bit 0: HW Interrupt On: W                                   |    |

| Bit 1: Allow Broadcast: W                                   |    |

| Bit 2: Internal Loop Back: W                                |    |

| Bit 3: mRT Mode: W                                          |    |

| Bit 4: Signal Generator Mode On: W                          |    |

| Bit 5: Clock (Clk) Trigger Enable: W                        |    |

| Bit 6: Force External Trigger In: W                         |    |

| Bit 7: Force External Trigger Out: W                        | 21 |

| Bit 8: Read IRIG Time                                       | 21 |

| Bit 9: Zero Time-Tag: W                                     | 21 |

| Bit 10: Set Time-Tag: W                                     | 21 |

| Bit 11: Read Time-Tag: W                                    | 21 |

| Bit 12: Use External Signal:W                               |    |

| Bit 13: Ext Input Clk = 1 MHz : W                           |    |

| Bit 14: Ext Input Clk = 5 MHz: W                            |    |

| Bit 15: Ext Input Clk = 10 MHz: W                           | 22 |

| Bit 16: RS-485 Trigger In Enable: W22                    |   |

|----------------------------------------------------------|---|

| Bit 17: RS-485 Trigger Out Enable: W22                   |   |

| Bit 18: Link Spec Mode (EBR Products Only): W22          |   |

| Bit 19: SDISC Trigger: W22                               |   |

| Bit 21: PB (Playback) Time Write: W23                    |   |

| Bit 22: Trig (Trigger) In Active Low to High: W23        |   |

| Bit 23: Gen (Generate) Trig (Trigger) on Decode Event: W |   |

| Bit 24: TX B Inhibit23                                   |   |

| Bit 25: TX A Inhibit23                                   |   |

| Bit 26: Bus B Only: W23                                  |   |

| Bit 27: Bus A Only23                                     |   |

| Bit 29: INT on BIT Fail :W24                             |   |

| Bit 30: Run Initiated BIT: W24                           |   |

| Bit 31: Reset Channel: W24                               |   |

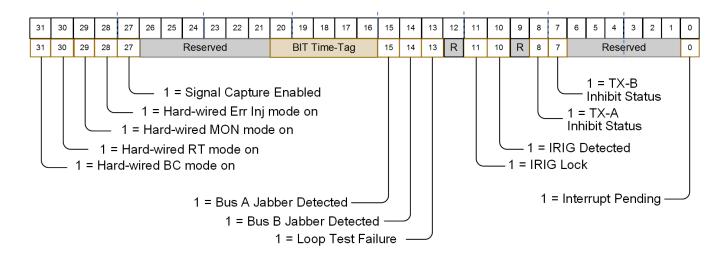

| Root PE Status Word24                                    |   |

| Figure Root PE-3: Root PE Status Word24                  |   |

| Bit 0: Interrupt Pending: W25                            |   |

| Bit 10: IRIG Detected: R25                               |   |

| Bit 11: IRIG Lock: R                                     |   |

| Bit 13: Loop Test Failure: R25                           |   |

| Bit 14: Bus B Jabber Detected: R25                       |   |

| Bit 15: Bus A Jabber Detected: R26                       |   |

| Bits 16-20: Bit Time Tag: R                              | ļ |

| Bit 27: Signal Capture Enabled: R26                      |   |

| Bits 28-31: Hard-wired Functional Status26               | ļ |

| Root PE Total Mon Command Counter: W: 0x000C26           | ļ |

| Root Total Mon Error Counter: W: 0x001027                |   |

| Root BM/BC Response Timeout: W: 0x001427                 |   |

| Root RT Mode (1553A/B Settings for RTs): W: 0x001827     |   |

| Root Time High & Time Low: W: 0x001C/2027                |   |

| Root IRIG Time High & Low: 0x0024/2827                   | , |

| Figure Root PE-4:IRIG Time Register Format               | 28 |

|----------------------------------------------------------|----|

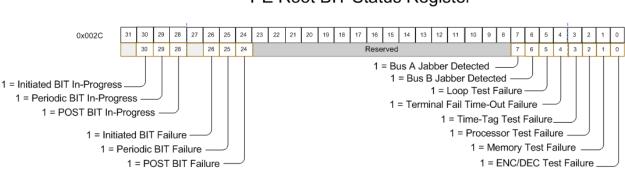

| Root BIT Status: 0x002C                                  | 29 |

| Figure Root PE-5: BIT Status Register                    | 29 |

| Bit 0: Encoder/Decoder Test Failure                      | 29 |

| Bit 1: Memory Test Failure                               | 29 |

| Bit 2: Processor Test Failure                            | 29 |

| Bit 3: Time-Tag Test Failure                             | 29 |

| Bit 4: Terminal Fail Timeout Failure                     | 29 |

| Bit 5: Loop Test Failure                                 | 29 |

| Bit 6: Bus B Jabber Detected                             | 30 |

| Bit 7: Bus A Jabber Detected                             | 30 |

| Bit 24: POST BIT Failure                                 | 30 |

| Bit 25: Periodic BIT Failure                             | 30 |

| Bit 26: Initiated BIT Failure                            | 30 |

| Bit 28: POST BIT In-Progress                             | 30 |

| Bit 29: Periodic BIT In-Progress                         | 30 |

| Bit 30: Initiated BIT In-Progress                        | 30 |

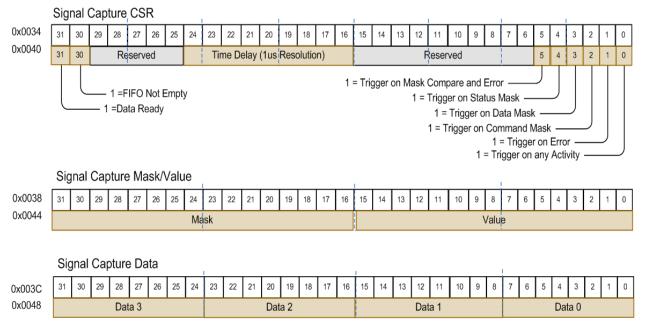

| Signal Capture Discussion                                | 31 |

| Figure Root PE-6: Signal Capture Registers               |    |

| Root Signal Capture CSR Bus A: 0x0034                    | 32 |

| Bit 0: Trigger on Any Activity: W                        | 32 |

| Bit 1: Trigger on Any Error: W                           | 32 |

| Bit 2: Trigger on Command Mask (Command Word – BC): W    | 32 |

| Bit 3: Trigger on DATA Mask: W                           | 32 |

| Bit 4: Trigger on STATUS Word Mask (Status Word - RT): W | 32 |

| Bit 5: Trigger on Error with Mask: W                     | 32 |

| Bits 16-24: Trigger Position: W                          |    |

| Bit 30: FIFO Not Empty                                   |    |

| Bit 31: Data Ready: W                                    | 33 |

| Root Signal Data A: 0x003C                               |    |

| Bits 0-7: Data 0                                         | 33 |

| Bits 8-15: Data 1                                             |    |

|---------------------------------------------------------------|----|

| Bits 16-23: Data 2                                            | 33 |

| Bits 24-31: Data 3                                            |    |

| Root Signal Capture CSR Bus B: 0x0040                         |    |

| Root Signal Data B: 0x0044                                    | 33 |

| Root Signal Data B: 0x0048                                    | 33 |

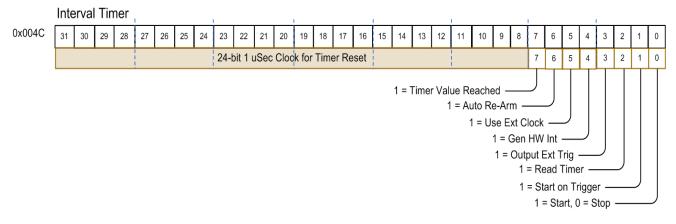

| Root Interval Timer: 0x004C                                   |    |

| Figure Root PE-7: Interval Timer Register                     | 34 |

| Bit 0: Timer Start/Stop: W                                    | 34 |

| Bit 1: Start on Ext Trig: W                                   | 34 |

| Bit 2: Read Timer: W                                          | 34 |

| Bit 3: Output Ext Trig: W                                     | 34 |

| Bit 4: Gen HW Int: W                                          | 34 |

| Bits 5: Use External Clock: W                                 | 35 |

| Bits 6: Auto Re-Arm: W                                        | 35 |

| Bits 7: Time Value Reached: W                                 | 35 |

| Bits 8-31: Time Interval Reset Value: W                       | 35 |

| PTP IEEE-1588 Registers                                       |    |

| API Hardware Interrupt: 0x00E0                                |    |

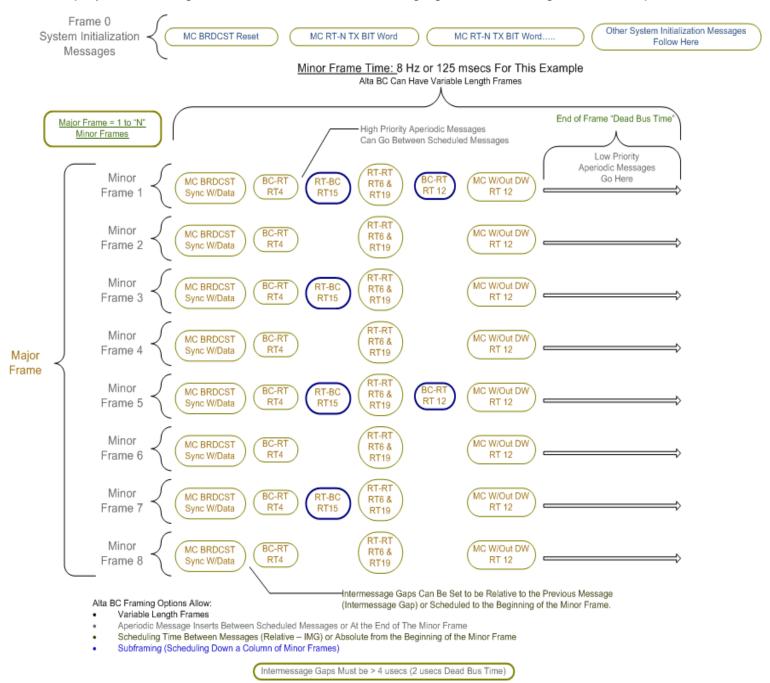

| AltaCore-1553 Bus Controller (BC)                             |    |

| BC Data Structures                                            |    |

| BC Basics                                                     |    |

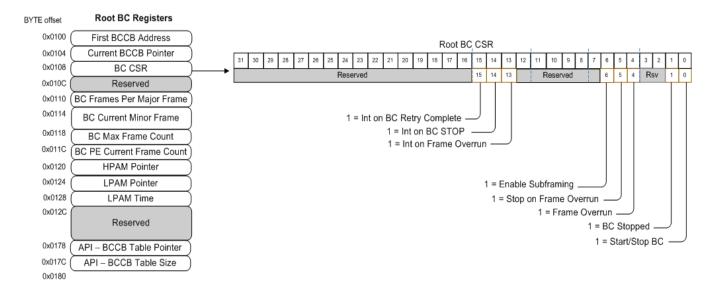

| Figure BC-1: Root BC Registers and Root BC CSR                |    |

| Root First BCCB Address: W: 0x0100                            |    |

| Root Current Transmission BC Control Block Pointer: W: 0x0104 | 39 |

| Root BC Control and Status Register: W: 0x0108                |    |

| Bit 0: Start/Stop BC: W                                       | 39 |

| Bit 1: BC Stopped                                             |    |

| Bit 4: Frame Overrun: W                                       | 39 |

| Bit 5: Stop of Frame Overrun: W                               | 40 |

| Bit 6: Enable Subframing: W                                   | 40 |

| Bit 13: Interrupt on Frame Overrun: W 40                        | ) |

|-----------------------------------------------------------------|---|

| Bit 14: Interrupt on BC Stopped: W 40                           | ) |

| Bit 15: Interrupt on Retry Complete: W40                        | ) |

| Root BC Frames Per Major Frame: W: 0x0110 41                    |   |

| Root BC PE Current Minor Frame Count : 0x011441                 |   |

| Root BC Max Frame Count : W: 0x0118                             |   |

| Root BC PE Current Total Frame Count: 0x011C41                  |   |

| Root High Priority Aperiodic Message: W: 0x012041               |   |

| Root Low Priority Aperiodic Message (LPAM) Pointer: W: 0x012442 | ) |

| Root LPAM Time: W: 0x0128                                       | 3 |

| API - BCCB Table Pointer: W: 0x0178                             | 5 |

| API - BCCB Table Size: W: 0x017C                                | ŀ |

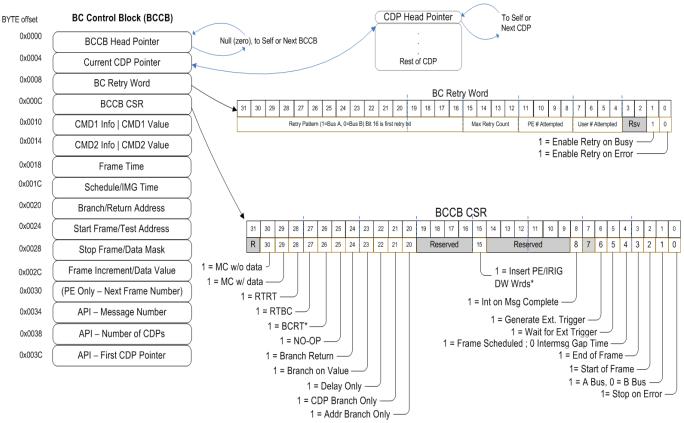

| BC Control Blocks (BCCB) – Extended Memory 44                   | ŀ |

| Figure BC-2: BC Control Block44                                 | ŀ |

| BCCB Head Pointer: W: 0x000045                                  | ; |

| Current Common Data Packet (CDP) Pointer: W: 0x000445           | ; |

| BCCB Retry Word: W: 0x0008                                      | ; |

| Bit 0: Enable Retry on Error: W                                 | ; |

| Bit 1: Enable BC Retry on Busy Bit: W46                         | 5 |

| Bits 4-7: Retry # Attempted: W46                                | 5 |

| Bits 8-11: PE Retry # Attempted46                               | 5 |

| Bits 12-15: Retry Count: W46                                    | 5 |

| Bits 16-31: Retry Pattern: W46                                  | 5 |

| BCCB Control and Status Register: W: 0x000C 47                  | , |

| Bit 0: Stop On Error: W47                                       | , |

| Bit 1: Bus Indicator: W47                                       | , |

| Bit 2: Start Frame Designator: W47                              | , |

| Bit 3: End of Frame Designator: W48                             | ; |

| Bit 4: Message Gap Type: W48                                    |   |

| Bit 5: Wait for External Trigger: W48                           | } |

| Bit 6: Generate External Trigger: W 49                          | ) |

|     | Bit 8: Interrupt on Message Complete: W                                                                   | . 50 |

|-----|-----------------------------------------------------------------------------------------------------------|------|

|     | Bit 15: Insert PE/IRIG in Data Words: W                                                                   | . 51 |

|     | Bit 20: Address Branch: W                                                                                 | . 52 |

|     | Bit 21: CDP Branch Only: W                                                                                | . 52 |

|     | Bit 22: Delay Only: W                                                                                     | . 54 |

|     | Bit 23: Branch: W                                                                                         | . 54 |

|     | Bit 24: Branch Return/Jump: W                                                                             | . 55 |

|     | Bit 25: NO-OP: W                                                                                          | . 55 |

|     | Bit 26: BC-RT: W                                                                                          | . 55 |

|     | Bit 27: RT-BC: W                                                                                          | . 55 |

|     | Bit 28: RT-RT: W                                                                                          | . 56 |

|     | Bit 29: Mode Code With Data Word: W                                                                       | . 56 |

|     | Bit 30: Mode Code Without Data Word: W                                                                    | . 56 |

|     | CMD1 Info   CMD1 value: W: 0x0010                                                                         | . 56 |

|     | CMD2 Info   CMD2 value: W: 0x0014                                                                         | . 56 |

|     | Frame Time: W : 0x0018                                                                                    | . 56 |

|     | Message Time Gap: W: 001C                                                                                 | . 57 |

|     | Address Branch/Return Address: W: 0x0020                                                                  | . 58 |

|     | Starting Frame   Frame Increment Word   Stop Frame: Test Address, Test Mask,<br>Test Data: W: 0x0024-002C | . 58 |

|     | Starting Frame: W: Test Address: 0x0024                                                                   | . 58 |

|     | Frame Increment: W: Data Mask: 0x0028                                                                     | . 59 |

|     | Frame Stop: W: Data Value: 0x002C                                                                         | . 59 |

|     | Subframing Discussion                                                                                     | . 59 |

|     | 16 LSB Next Frame Value: 0x0030                                                                           | . 60 |

|     | API – Message Number: 0x0034                                                                              | . 60 |

|     | API – Number of CDPs: 0x0038                                                                              | . 60 |

|     | API – First CDP Pointer: 0x003C                                                                           | . 60 |

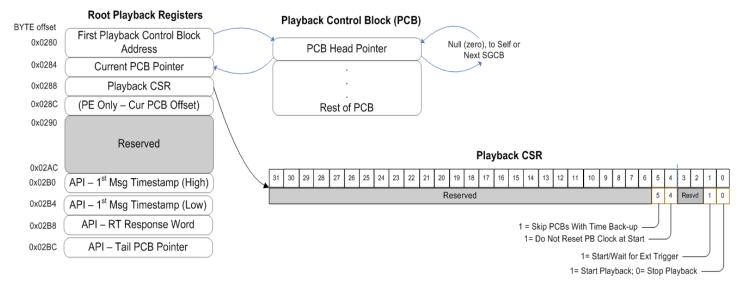

| Alt | aCore-1553 Playback (PB)                                                                                  | . 61 |

|     | Introduction                                                                                              | . 61 |

|     | Figure PB-1: Playback Root Registers                                                                      | . 61 |

| Playback Transmission Timing                               | . 62 |

|------------------------------------------------------------|------|

| PCB Timing Discussion – Relative Timing                    | . 63 |

| PCB Timing Discussion – Absolute Timing (AT)               | . 63 |

| Root First Playback Control Block Address: W: 0x0280       | . 64 |

| Root Current PCB Pointer: 0x0284                           | . 64 |

| Root Playback Control and Status Register (CSR): W: 0x0288 | . 64 |

| Bit 0: Start/Stop Playback: W                              | . 64 |

| Bit 1: Wait For Ext Trigger: W                             | . 64 |

| Bit 4: Do Not Reset PB Clock at Start: W                   | . 64 |

| Bit 5: Skip PCBs with Time Back-up: W                      | . 64 |

| API – 1 <sup>st</sup> Message Time High: 0x02B0            | . 65 |

| API – 1 <sup>st</sup> Message Time Low: 0x02B4             | . 65 |

| API – RT Response Word: 0x02BC                             | . 65 |

| API – Tail Pointer: 0x02C0                                 | . 65 |

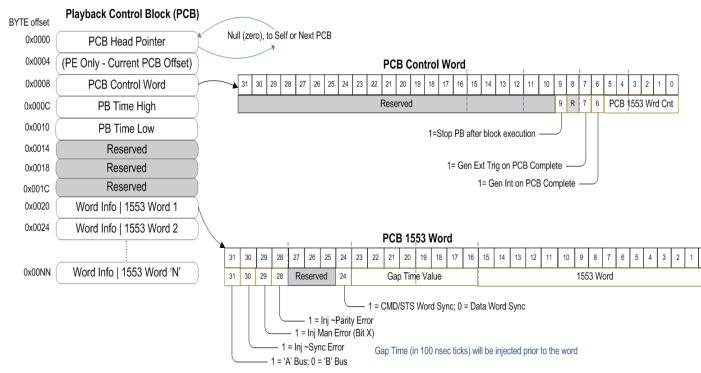

| Playback Control Blocks (PCBs)                             | . 65 |

| Figure PB-2: Playback Control Block (PCB)                  | . 66 |

| PCB Head Pointer: W: 0x0000                                | . 66 |

| Current PCB Offset – PE Only: 0x0004                       | . 66 |

| PCB Control Word: W: 0x0008                                | . 66 |

| Bits 0-5: PCB 1553 Word Count: W                           | . 66 |

| Bit 6: Gen Int on PCB Complete: W                          | . 66 |

| Bit 7: Gen Ext Trigger on PCB Complete: W                  | . 67 |

| Bit 8: Flash User LED on PCB Complete: W                   | . 67 |

| Bit 9: Stop PCB Execution: W                               | . 67 |

| PCB Time High & Low: W: 0x000C-0x0010                      | . 67 |

| 1553 Word Encoding: 0x0020-0x005F (Variable to 0x005F)     | . 67 |

| Bits 16-23: Gap Time Value                                 | . 67 |

| Bit 24: 1=Command/Status Word Sync; 0=Data Word Sync       | . 67 |

| Bit 28: Parity Error                                       | . 68 |

| Bit 29: Manchester Error                                   | . 68 |

| Bit 30: Sync Error                                         | . 68 |

| Bit 31: 1=A Bus; 0=B Bus                                 | 68 |

|----------------------------------------------------------|----|

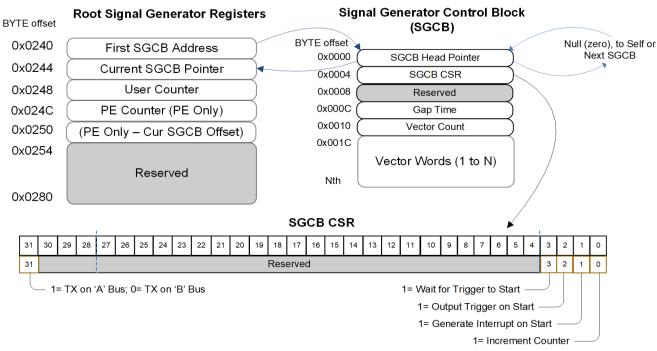

| AltaCore-1553 Signal Generator (SG)                      | 69 |

| Signal Generator                                         | 69 |

| Overview of Signal Generation                            | 69 |

| Figure SG-1: Signal Generator Data Structures            | 70 |

| Root PE Signal Generator Control Bits                    | 70 |

| 2-Bit, Bi-Level Vectors                                  | 70 |

| Root Signal Generator Registers                          | 71 |

| Root First SGCB Address: 0x0240: W                       | 71 |

| Root Current Signal Generator Address: 0x0244: R         | 71 |

| Root Signal Generator Count: 0x0248: W                   | 71 |

| Root PE Count: R: 0x024C                                 | 72 |

| Root PE Current Vector Location: R: 0x0250               | 72 |

| Root Reserved 0x0254-0x0280                              | 72 |

| Signal Generator Control Blocks (SGCB) – Extended Memory | 72 |

| Next SGCB Pointer: W: 0x0000                             | 72 |

| SGCB Control and Status Register: W: 0x0004              | 72 |

| Bit 0:                                                   | 72 |

| Bit 1:                                                   | 72 |

| Bit 2:                                                   | 72 |

| Bit 3:                                                   | 73 |

| Bit 31: Bus Selection Bit: W                             | 73 |

| Gap Time: W: 0x000C                                      | 73 |

| Vector Count: W: 0x0010                                  | 73 |

| SGCB Vector Bit Words: W: 0x0014-Variable                | 73 |

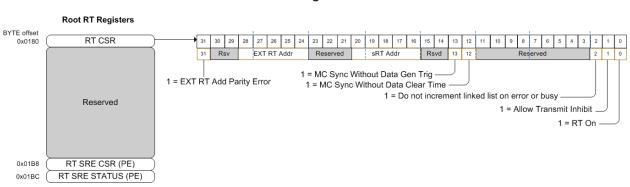

| AltaCore-1553 Remote Terminal (RT)                       | 74 |

| RT: Active and Map Monitor                               | 74 |

| Overview of RT Functions                                 | 74 |

| Single RT and Multi RT(mRT) Modes & 1760 Addressing      | 75 |

| Root RT CSR: W: 0x0180                                   | 75 |

| Bit 0: RT On/Off: W                                      | 75 |

| Bit 1: Transmit Inhibit Control: W                                                 | .75  |

|------------------------------------------------------------------------------------|------|

| Bit 2: Do Not Increment CDP Link List on Error or Busy: W                          | . 75 |

| Bit 12: MC Sync Without Data Clear Time Tag: W                                     | . 76 |

| Bit 13: MC Sync Without Gen Trig: W                                                | . 76 |

| Bits 16-20: Single RT Address: R                                                   | . 76 |

| Bits 24-28: RT Ext Address: R                                                      | . 77 |

| Bit 31: External RT Address Parity Error: R                                        | . 77 |

| Root RT Reserved Words: W: 0x0181-0x001BC                                          | . 77 |

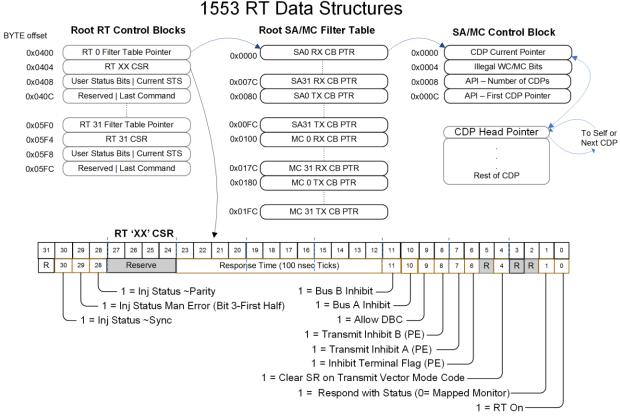

| Root RT Control Blocks (RTCBs): W: 0x0400-0x05FC                                   | . 77 |

| Figure: RT-2: RT Control Blocks, RTCB CSR and Filter Table                         | . 78 |

| RT XX Filter Table Pointer: W: 0x0000                                              | . 78 |

| RTCB CSR: W: 0x0004                                                                | . 78 |

| Bit 0: RT On/Off: W                                                                | . 78 |

| Bit 1: RT Active/Map Monitor: W                                                    | . 78 |

| Bit 4: Clear Service Request (SR) Bit on Transmit Vector Mode Code: W              | .79  |

| Bit 6: Inhibit Terminal Flag                                                       | . 79 |

| Bit 7: Transmit Inhibit A: W                                                       | .79  |

| Bit 8: Transmit Inhibit B: W                                                       | . 79 |

| Bit 9: Allow Dynamic Bus Control (DBC) Mode Code Control: W                        | . 79 |

| Bit 10: Bus A Inhibit: W                                                           | . 80 |

| Bit 11: Bus B Inhibit: W                                                           | . 80 |

| Bits 12-23: Response Time Setting: W                                               | . 80 |

| Bits 28: Inject Status Word Inverted Parity: W                                     | . 80 |

| Bits 28: Inject Status Word Manchester Encoding Error on Bit X: W                  | . 80 |

| User Status Word Bits   Last Status Word: W: 0x0008                                | . 81 |

| Last Command Word: W: 0x000C                                                       | . 81 |

| RT Filter Table – Extended Memory                                                  | . 81 |

| Subaddress/Mode Code Control Blocks (SA/MC) – Extended Memory                      | . 82 |

| SA/MC-CDP Head Pointer: W: 0x0000                                                  | . 82 |

| SA/MC Word Count Legalization Settings   Legal Word Count for Mode Code: W: 0x0004 | . 82 |

| SA/MC Filter Table – SA Legal Word Counts                  |    |

|------------------------------------------------------------|----|

| Legalization of Mode Code: W                               |    |

| Mode Code 0 (Dynamic Bus Control)                          |    |

| Mode Code 1 (Synchronize)                                  | 83 |

| Mode Code 2 (Transmit Status Word)                         | 83 |

| Mode Code 3 (Initiate Self Test)                           | 83 |

| Mode Code 4 (Transmitter Shutdown)                         | 83 |

| Mode Code 5 (Override Transmitter Shutdown)                | 83 |

| Mode Code 6 (Inhibit Terminal Flag)                        | 83 |

| Mode Code 7 (Override Inhibit Terminal Flag)               | 83 |

| Mode Code 8 (Reset RT)                                     | 83 |

| Mode Code 16 (Transmit Vector Word)                        | 83 |

| Mode Code 17 (Synchronize with Data)                       | 83 |

| Mode Code 18 (Transmit Last Command)                       |    |

| Mode Code 19 (Transmit BIT Word)                           |    |

| Mode Code 20 (Selected Transmitter Shutdown)               | 84 |

| Mode Code 21 (Override Selected Transmitter Shutdown       |    |

| Two Reserved Words for Future Use: 0x0008/C                | 84 |

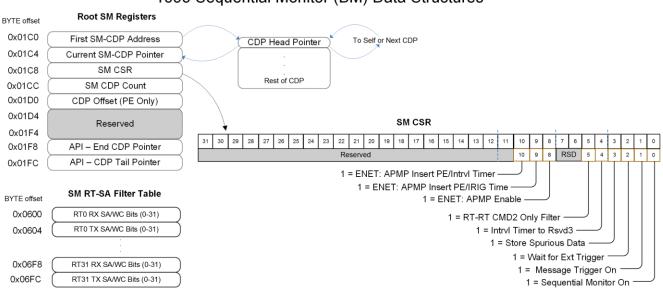

| AltaCore-1553 Sequential Monitor (SM/BM)                   | 85 |

| Sequential Monitor (SM) – Bus Monitor (BM)                 | 85 |

| Figure SM-1: Root and Extended SM Data Structures          | 85 |

| ENET-1553 APMP                                             | 85 |

| Root First SM-CDP Address: W: 0x01C0                       | 85 |

| Root Current SM-CDP Pointer: W: 0x01C4                     | 85 |

| Root SM CSR: W: 0x01C8                                     | 86 |

| Bit 0: SM On/Off: W                                        | 86 |

| Bit 1: Trigger from CDP On/Off: W                          | 86 |

| Bit 2: External Trigger On/Off: W                          | 86 |

| Bit 3: Store Spurious Data On/Off: W                       |    |

| Bit 4: Store Interval Timer Value in CDP Reserve Word 3: W | 86 |

| Bit 5: RT-RT CMD2 Only Filter: W                           | 87 |

|                                                            |    |

| Bit 8: ENET APMP Enable                                            |    |

|--------------------------------------------------------------------|----|

| Bit 9: ENET APMP Insert PE/IRIG Time                               |    |

| Bit 10: ENET APMP Insert PE/Interval Timer                         |    |

| Root SM-CDP Count Register (Sequence Number): W: 0x01CC            |    |

| API – CDP End Pointer: W: 0x01F8                                   |    |

| API – CDP Tail Pointer: W: 0x01FC                                  |    |

| Root RT/SA Filter Words: W: 0x0600 to 0x06FC                       |    |

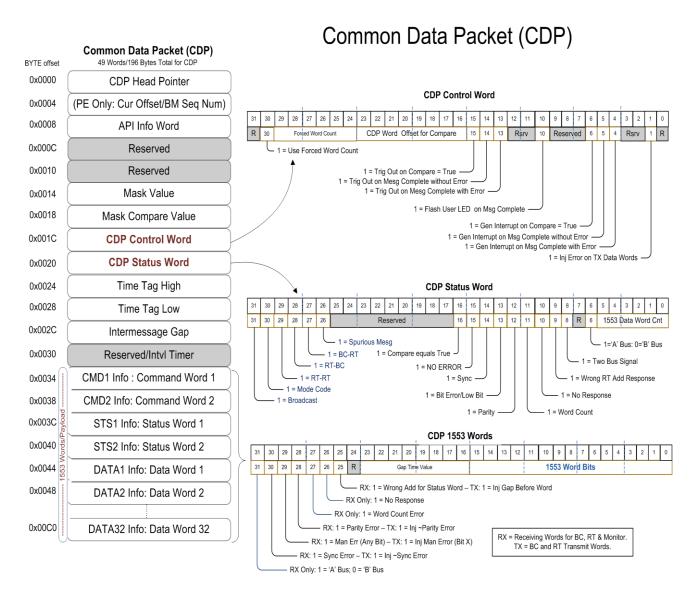

| AltaCore-1553 Common Data Packet (CDP)                             |    |

| Common Data Packet - Extended Memory                               |    |

| Figure CDP-1: CDP Data Structures                                  |    |

| CDP Update Status – How to Sync Your Application to Fresh CDP Data | 91 |

| Next CDP Pointer : W: 0x0000000                                    | 91 |

| Current CDP Offset (PE Only)/BM Counter Sequence Number: 0x0004    |    |

| API Info Words: 0x0008-0x0010                                      |    |

| Mask Value: W: 0x0014                                              |    |

| Mask Compare Value: W: 0x0018                                      |    |

| CDP Control Register: W: 0x001C                                    |    |

| Bit 1: Injection Error on Transmit Message On/Off: W               |    |

| Bit 4: Gen Interrupt on Message Complete with Error: W             |    |

| Bit 5: Gen Interrupt on Message Complete Without Error: W          |    |

| Bit 6: Gen Interrupt of Word Mask On/Off: W                        |    |

| Bit 10: Flash LED on Message Complete: W                           |    |

| Bit 13: Trigger Out on Message Complete with Error: W              |    |

| Bit 14: Trigger Out on Message Complete Without Error: W           | 94 |

| Bit 15: Trigger Out on Mask/Value Positive: W                      |    |

| Bits 16-23: Word Offset for Compare Function: W                    |    |

| Bit 24-29: Forced Word Count: W                                    |    |

| Bit 30: Enable Force Word Count: W                                 |    |

| CDP Status Word: 0x0020                                            |    |

| Bits 0-5: Actual Data Word Count                                   |    |

| Bit 6: Bus Indicator                                               |    |

|    | Bit 8: Two Bus                                 | . 95 |

|----|------------------------------------------------|------|

|    | Bit 9: Wrong RT Address Response               | . 95 |

|    | Bit 10: No Response                            | . 96 |

|    | Bit 11: Word Count                             | . 96 |

|    | Bit 12: Parity                                 | . 96 |

|    | Bit 13: Bit Error/Low Bit                      | . 96 |

|    | Bit 14: Bad Sync Detected                      | . 96 |

|    | Bit 15: No Error Detected/Message Complete     | . 96 |

|    | Bit 16: Compare Equals True                    | . 96 |

|    | Bit 26: Spurious Data                          | . 96 |

|    | Bit 27: BC-RT                                  | . 97 |

|    | Bit 28: RT-BC                                  | . 97 |

|    | Bit 29: RT-RT                                  | . 97 |

|    | Bit 30: Mode Code                              | . 97 |

|    | Bit 31: Broadcast                              | . 97 |

| Т  | ime Tag High/Time Tag Low: 0x0024 & 0x0028     | . 97 |

| Ir | termessage Gap: 0x002C                         | . 97 |

| R  | eserved/Interval Timer: 0x0030                 | . 98 |

| С  | DP 1553 Words (Message Payload): 0x0034-0x00C0 | . 98 |

| Ir | fo RX Bit Values (16 MSB) for 1553 Words       | . 99 |

|    | Bits 16-23: Gap Time Value                     | . 99 |

|    | Bit 25: Wrong Status Address                   | . 99 |

|    | Bit 26: No Response                            | . 99 |

|    | Bit 27: Word Count Error                       | . 99 |

|    | Bit 28: Parity Error                           | . 99 |

|    | Bit 29: Manchester Error                       | 100  |

|    | Bit 30: Sync Error                             | 100  |

|    | Bit 31: 1=Bus A, 0=Bus B                       | 100  |

| Ir | fo TX Bit Values (16 MSB) for 1553 Words       | 100  |

|    | Bits 16-23: Gap Time Value                     | 100  |

|    | Bit 25: Inj Gap Before Word                    | 100  |

| Bit 28: Parity Error                                                      | . 100 |

|---------------------------------------------------------------------------|-------|

| Bit 29: Manchester Error                                                  | . 100 |

| Bit 30: Sync Error                                                        | . 101 |

| CMD1 Info   CMD1 Value : 0x0034                                           | . 101 |

| CMD2 Info   CMD2 Value : 0x0038                                           | . 101 |

| STS1 Info   STS1 Value: 0x003C                                            | . 101 |

| STS2 Info   STS2 Value: 0x0040                                            | . 101 |

| Data Info N   Data Word N: 0x0044/BC                                      | . 102 |

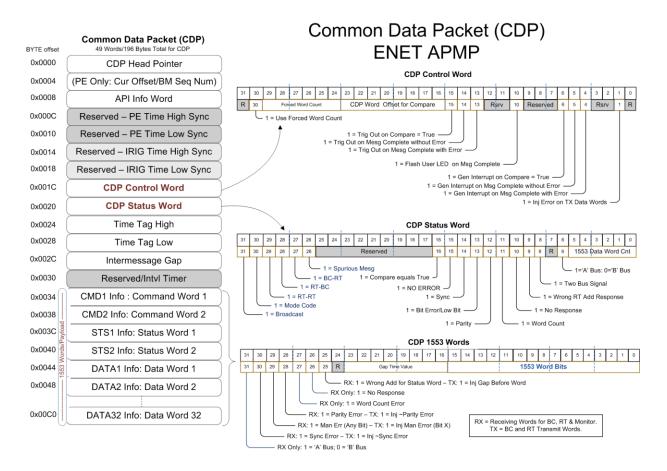

| ENET APMP CDP Format: PE + IRIG or Interval Timer Inserts                 | . 102 |

| Figure CDP-2: ENET APMP CDP Structure                                     | . 103 |

| AltaCore-1553 Interrupt Functions                                         | . 104 |

| Interrupt Functions                                                       | . 104 |

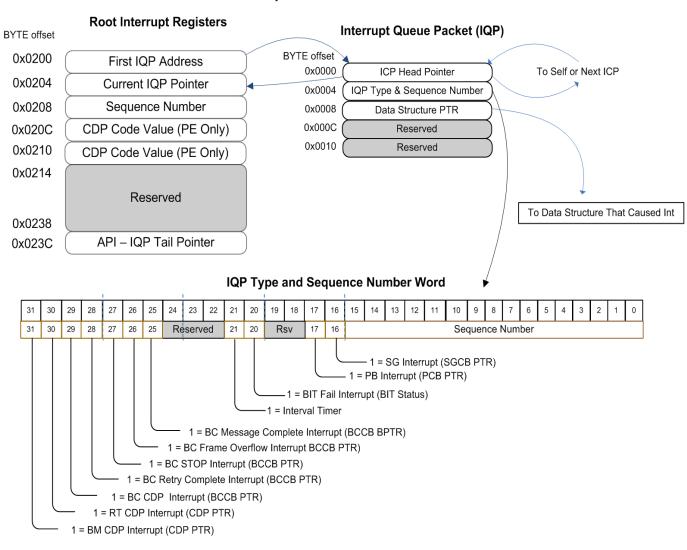

| Figure Int-1: Interrupt Data Structures                                   | . 104 |

| Root Starting Interrupt Queue Packet (IQP) Address: W: 0x0200             | . 105 |

| Root Current IQP Address: 0x0204                                          | . 105 |

| Root Interrupt Sequence Number (16 LSB Bits): W: 0x0208                   | . 105 |

| Root CDP Code Value (PE Only) – Reserved: 0x020C                          | . 105 |

| Root CDP Code Value (PE Only) – Reserved: 0x0210                          | . 105 |

| API – IQP Tail Pointer: 0x023C                                            | . 105 |

| Interrupt Queue Packets (IQP) – Extended Memory                           | . 105 |

| IQP Head Pointer: W: 0x0000                                               | . 106 |

| Interrupt Type (16 Bits)   Interrupt Sequence Number (16 Bits): W: 0x0001 | . 106 |

| Bit 16: SG Interrupt (SGCB PTR)                                           | . 106 |

| Bit 17: PB Interrupt (PBCB PTR)                                           | . 106 |

| Bit 20: BIT Fail Interrupt (BIT Status)                                   | . 106 |

| Bit 21: Interval Timer                                                    | . 106 |

| Bit 25: BC Message Complete Interrupt (BCCB Pointer)                      | . 107 |

| Bit 26: BC Frame Overflow Interrupt (BCCB Pointer)                        | . 107 |

| Bit 27: BC Stop Interrupt (BCCB Pointer)                                  | . 107 |

| Bit 28: BC Retry Complete Interrupt (BCCB Pointer)                        | . 107 |

| Bit 29: BC CDP Interrupt (CDP Pointer)                                    | . 107 |

| Bit 30: RT CDP Interrupt (CDP Pointer) 10 | )7 |

|-------------------------------------------|----|

| Bit 31: BM CDP Interrupt (CDP Pointer)10  | )7 |

| Data Structure Pointer: W: 0x000210       | )7 |

| Revision Information10                    | )8 |

Blank Page

<~~~>

## AltaCore-1553™ Document Introduction

#### Introduction

This document is the Specifications/User's Manual Document for Alta Data Technologies' (ADT) *AltaCore-1553* Notice II-IV compliant protocol engine (PE) product (and supports most pre-notice II standard derivations, such as 1553A). This document specifies the design of the product and provides an overview for the reader who wants a detailed understanding of the PE 1553 design. The reader should also reference the *AltaAPI* manual (found on the CD or Alta web site) and source code for detailed descriptions of the software/backplane interface to *AltaCore*.

**NOTE:** For most customer applications, the PE's design and processes are transparent to the application as the *AltaAPI* manages PE setup and execution. Most customers can skip this entire manual and simply refer to the *AltaAPI* manual and example programs, and their respective Hardware Manual for their 1553 application requirements. It is also recommended that the reader review *AltaView* and *AltaRTVaI* products to learn about advanced avionics analyzers and validation products.

This document is divided into sections that describe the major data structures of *AltaCore-1553*:

- Introduction (This Section)

- Global Registers (Card Level)

- PE Channel Root Registers (Channel/Device Level)

- Bus Controller (BC)

- o Playback (PB)

- Signal Generator (SG)

- Remote Terminal (including Map Monitor RT)

- Sequential Monitor (SM or Bus Monitor BM)

- Common Data Packet (CDP)

- Interrupts (Int)

This Introduction section provides an overview of the *AltaCore* architecture and should be reviewed before diving deeper in to the data structures sections.

#### Terminology

This manual assumes the reader is very familiar with the 1553B Notice II standard and popular variants. Please see the Alta web site to download our tutorial and reference and the 1553B standard (and obtain links to the SAE site to purchase the latest version).

- msec = milli seconds; μsec = micro seconds; ηsec = nano seconds.

- An Alta card/board can contain one or more devices

- A *device* is an independent functional unit. Each 1553 *channel* is a *device*

- A 1553 *channel* is a complete dual-redundant interface (with bus A and bus B connections) to the 1553 bus

- The AltaCore-1553 Protocol Engine (PE) implements the 1553 protocol for an individual 1553 channel

- When discussing "Global" registers or values, these apply to ALL channel/devices. The term "ROOT" register or value is for a channel/device.

#### **AltaCore-1553** Architecture and Document Basics

*AltaCore* is a 32-bit based PE that supports 1-4 1553 dual redundant, independent channels. The pure FPGA 32-bit base design greatly enhances backplane/processor throughput as compared to most 16-bit 1553 interfaces. *AltaCore* has a Common Data Packet (CDP) data structure, which as its name suggests, is a common data structure for BC, RT and Monitor data buffers. CDP's provide maximum flexibility between 1553 functions and greatly reduces host application complexity – reducing integration time. Each of *AltaCore*'s BC, RT, Monitor and Interrupt functions have several execution options to provide the most advanced 1553 interface available on the market.

#### **Memory Mapped Architecture**

The *AltaCore* protocol engine (PE) utilizes dedicated on-chip (FPGA on-chip memory) and/or on-board Extended Memory (depending on the configuration).

The memory of the PE/Card appears as a contiguous memory map to the host backplane regardless of the on-chip or on-board configuration (additional PE FPGA logic provides the arbitration for host access and various PE channel access). For most Alta card designs, an *AltaCore* product uses high speed Quad Data Rate RAM, but the design is flexible to be integrated to most common RAM bus architectures.

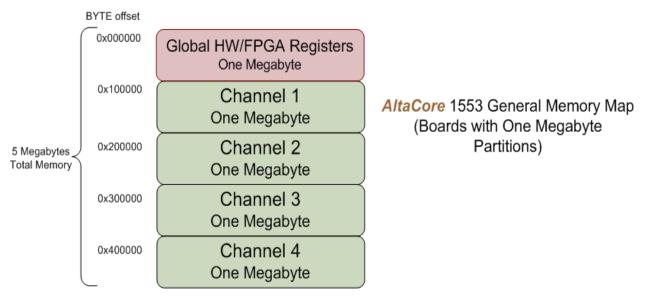

The *AltaAPI* or customer's application addresses each 1553 channel through memory offset or software pointer schemes. The *AltaAPI* User's manual provides details of host driver and memory mapping requirements. Your Alta Product Hardware Manual (on the CD or the Alta web site download) details the memory configuration for your product (most card level products have one megabyte of dedicated on-board memory per 1553 channel), pin-outs and special configurations. Figure Intro-1 show the basic memory mapping configuration for a 4 channel 1553 interface with one megabyte of RAM per channel (standard configuration for most PCI, PCI Express, PMC, cPCI, etc... -MA4 models only have 512K bytes per 1553 channel). Special configurations may vary.

Figure Intro-1: Basic AltaCore Memory Map

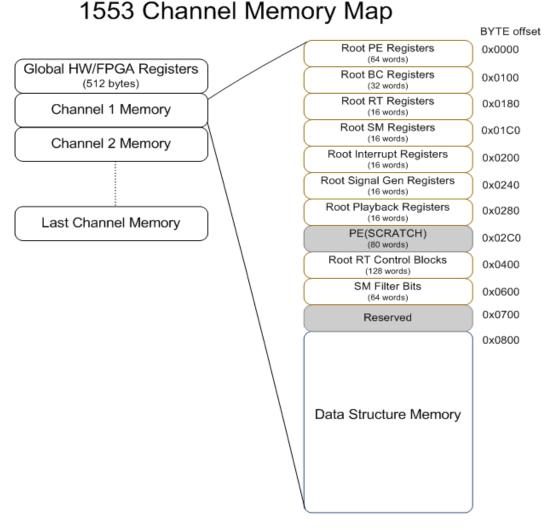

#### **Root Data Structures**

Each of the major data structure elements (BC, RT, Monitor and Interrupt) begins with setup words known as *ROOT* registers. Each channel has a common Root register set called PE Channel Root registers that provide setup and control information for all 1553 functions of that channel. Each of the 1553 functions of a channel also have a Root register set that provides the base setup and address pointers to data structures to control the respective 1553 function and buffer the bus data (in CDPs). (Root registers reside in the FPGA on-chip memory and have fixed address offsets relative to the card's and channel's base address.)

#### BC, RT, Monitor and Interrupt Data Structures: Control Blocks, CSRs and CDPs

BC (including Signal Generation and Playback), RT, Sequential Monitor and Interrupt functions have two levels of data structures that control execution: Root Registers and Control Blocks (in extended, on-board memory) that direct sub-functions and provide 1553 data buffering. Each Root level function and respective Control Block have Control and Status Registers (CSR's) that provide setup options and execution feedback. Control Blocks for each function will reference (point to) linked-list Common Data Packets (CDPs) that provide 1553 data buffering and time stamping. (Most of these data structures reside in on-board high speed RAM memory external to the FPGA.)

All options and data structures are detailed in the following sections.

**NOTE:** Several data structures of the PE are pointers to other tables or buffer data structures. The user must take great care to never populate a utilized structure with a null pointer or improper value (a value outside the on-board memory range). For example, if an RT is turned-on for responses and the Root or secondary pointer arrays are not properly programmed, then the PE will have unpredictable results (like any design that has a bad pointer reference). The PE will not check for null or improper values and bad pointers will cause unpredictable behavior. The *AltaAPI* properly manages and provides allocation/destruction functions for the user application.

#### **Memory Offset References**

Memory references in this document are in byte offsets. The PE memory (a common word) is a 32-bit atomic machine, 4-byte aligned.

#### Packed Word and Bit Data Structures

*AltaCore* data structures are typically packed 32-bit word structures that may have embedded packed bit or single bit settings. The right most bit is LSB bit 0 (zero) and the left most bit is MSB 31. The general rule is that a bit value of 1 (one) is an "on/set/positive" and a 0 (zero) is "off/clear/negative."

All data structures will be labeled "**W**" (Write) if the user's application (or *AltaAPI*) has the capability to write the value of the respective data element (word, bit or packed bits). Unless noted in the description, assume all data structures may be read by the user's application. The safest way to set control bits is to read the respective CSR/Register and OR in the selected bits and then write back. Great care must be taken to not set or change values of active registers during execution.

#### **Execution Times, Bus Timing, Time Tags**

Execution times provided herein are respective to the PE and do not include backplane transfer times. In general, after execution of a transmit function, the user should allow 10 µsecs settling time (process overhead) for accurate future transmission timing (for example, the user needs to provide 10 µsecs of non-activity at the end of a BC minor frame to assure accurate Minor Frame/Minor Frame timing to 500 ŋsec). There are some special cases that require more than 10 µsecs and the reader should reference the respective section for detailed timing requirements. Generally, Intermessage Gap times of 4-6 µsecs are required for extremely accurate BC, Playback and Signal Generation Timing.

The user will have several options for programming gaps (dead bus between words or messages). These values are typically 32-bit, 100 nsec tick values.

All BC, RT and Monitor functions have data packet time stamps (a time value placed on the message when decoded) and these are 64-bit, 20nsec time ticks (stored in two 32-bit words – Time High & Low).

#### **Reserve Bits and Words**

Many bits and words are "Reserved" for future use or are used by the PE execution. All Reserved BITS should assume a value of zero. Reserve Words should not be written to. If a reserve word is part of a larger data structure word packet, assume a value of zero for initialization, but then do not write to this word. For updating packed bit-word structures, the user's application should first read the word and then logically OR-in the desired one bits (or AND-out the zero bits) and then write back to the same location (please see the *AltaAPI* source for numerous examples) The API source code is provided and provides the proper set and rules for memory access – for custom applications, please use the API as a design guide.

#### **Figure Color Codes**

In the following figures, a brown outline/white box signifies a bit/word/area that is programmed by the User. The light gray is usually a reserved bit/word/area and should not be changed by the user (the PE will update or use this element for processing). The CDP diagrams show mixed brown/gray words that are update by both the PE and User programming. Most gray/reserved areas should be set to zero and most of these areas can be read by the user without affecting PE processing.

## AltaCore-1553 Global Card Level Registers

#### **Global Card Level Registers**

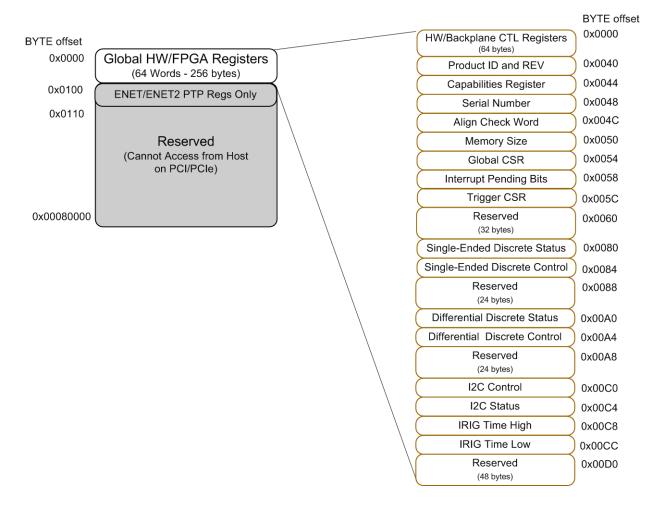

The area that occupies the first mega byte of the card memory map contains backplane and global card level settings and status values that affect processing for all channels. This area also contains the digital discrete, time and Built-In-Test (BIT) settings and values of the card.

## Global Hardware (PE) Setup/Control/Int Registers

Figure Global Registers-1: Global Card Level Registers

#### HW/Backplane CTL Registers (16 words - 0x00000000-0000000F)

The first 16 words of the memory map are reserved for backplane configuration registers. Please see your product's Hardware Manual for details on these registers.

## **Global Registers**

| Trigger Input Status | Trigger Output Control |

|----------------------|------------------------|

|                      |                        |

<sup>\*</sup>Note: See your hardware manual for trigger assignments.

# Global Registers (cont.)

| ()                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Single-Ended Discrete Status Register – 0x00000080                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0   |

| Bi-Directional Discrete Input Status (1=not active, 0=active)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| Single-Ended Discrete Output Register – 0x00000084                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 31       30       29       28       27       26       25       24       23       22       21       20       19       18       17       16       15       14       13       12       11       10       9       8       7       6       5       4       3       2       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0   |

| Bi-Directional Discrete Output Control (1=drive output low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Ľ   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| Differential Discrete Status Register – 0x000000A0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0   |

| Discrete Input Status (1=active, 0=not active)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| Differential Discrete Output Register – 0x000000A4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| Output Enable (1=Enable Transmit)     Output Control (1 = drive output high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| *Note: The number of single-ended and differential discretes varies from board to board. See individual board HW manuals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | for |

| details on discrete counts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 101 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |